# SIX CHANNEL TRANSIENT RECORDER

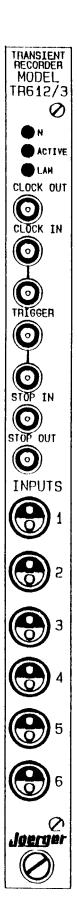

MODEL TR612/3

# MODEL TR612/3

# SIX CHANNEL, 3MHZ, 12 BIT TRANSIENT RECORDER WITH "FASTCAMAC" READ

#### **FEATURES:**

- SIX INDEPENDENT, 3MHZ, 12 BIT TRANSIENT RECORDERS

- INDIVIDUAL ADC AND SAMPLE AND HOLD PER CHANNEL

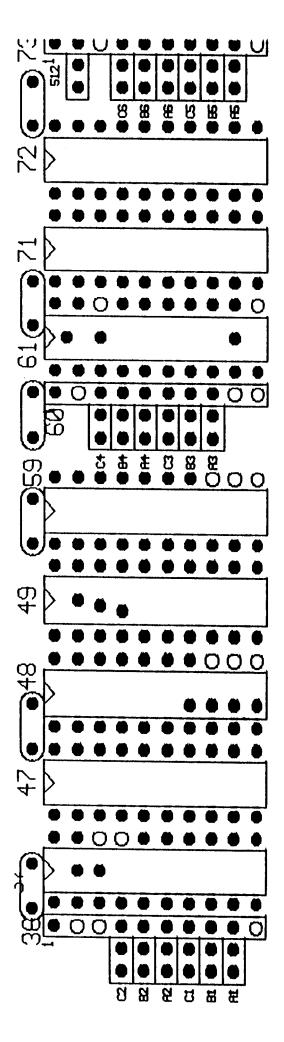

- 128K SRAM PER CHANNEL, 512K OPTIONAL

- "FASTCAMAC" READ

- ACTIVE MEMORY SIZE PROGRAMMABLE

- SINGLE WIDTH "CAMAC" MODULE

- BURST AND PRE/POST TRIGGERING MODES SELECTABLE

- INTERNAL CRYSTAL OSCILLATOR OR EXTERNAL CLOCK SELECTABLE

- OPERATING SPEED PROGRAMMABLY SET

- FULL AMPLITUDE BANDWIDTH OF 5MHZ

- ACQUISITION TIME FOR FULL SCALE STEP IS 150NS TYPICAL

- EACH CHANNEL FILTERED AND ISOLATED FOR IMPROVED PERFORMANCE AND HIGH CHANNEL CROSSTALK REJECTION

#### **APPLICATIONS:**

- ECONOMICAL HIGH PERFORMANCE MULTICHANNEL TRANSIENT RECORDING

- FULL PROGRAMMABILITY WITH LARGE INTERNAL MEMORY AND "FASTCAMAC" READ OFFERS VERSATILE SOLUTIONS FOR MANY APPLICATIONS

JOERGER ENTERPRISES, INC. MODEL TR612/3 is a high performance, six channel, 12 bit recorder packaged in a single width "CAMAC" module. Each channel is completely independent with its own 12 bit ADC, sample and hold amplifier and SRAM. The Model TR612/3 operates at 3MHZ with 128K or 512K of SRAM per channel. Data is read in block mode using F2(Ax) or for high speed applications the new "FASTCAMAC" read protocol has been added. This uses command F5(Ax) and a series string of S1 pulses at a rate of up to 2.5Mhz per word greatly enhancing readout speed. To insure accurate results each channels input differential amplifier offers high input impedance, a full power bandwidth of 5MHz and can acquire a full scale input in less than 150nsec's. These characteristics are often overlooked and the only important characteristic noted is the recording speed. However, the full signal must get to the ADC whether it be sinusoidal or pulse type or more likely a combination. The input ranges are  $\pm 10v$ ,  $\pm 5v$ ,  $\pm 2.5v$ , 0 to +10v and 0 to +5v. An internal crystal oscillator is provided and the module can also accept an external clock. The clock source is programmably selected as is the active frequency used. The module can operate in burst or pre/post trigger modes. The record mode and the active memory size are programmably selected to satisfy the current application. Great care has been taken to reduce noise susceptibility and channel crosstalk. The power to each channel's analog section is filtered and separate grounds are used. This approach has made our "VME" and CAMAC recorders very successful.

### SPECIFICATIONS (for each channel)

INPUT RANGE  $\pm 10v$ ,  $\pm 5v$ ,  $\pm 2.5v$ , 0 to  $\pm 10v$ , 0 to  $\pm 5v$  (shipped  $\pm 5v$ )

INPUT IMPEDANCE 1Mohms, differential

ANALOG BANDWIDTH 5MHZ for full scale input, 20 MHZ small signal bandwidth

ACCURACY  $\pm .05\%$  of full scale

APERTURE JITTER 40psec

SAMPLING RATE 3MHZ maximum

RESOLUTION 12 bits, no missing codes

MEMORY 128K SRAM standard, 512K optional

EXTERNAL CLOCK IN TTL, 3MHZ max., can be daisy chained,  $500\Omega$  to ground

CLOCK OUT Active clock out, TTL

TRIGGER IN TTL pulse input, can be daisy chained,  $500\Omega$  to ground

STOP IN TTL pulse input, can be daisy chained,  $500\Omega$  to ground

STOP OUT Directly connected to Stop In, used for daisy chaining

#### CAMAC COMMANDS

| COMMAND       | Q | FUNCTION                                                                |

|---------------|---|-------------------------------------------------------------------------|

| 00,01         | 1 | Reads active memory size, operating mode, pre/post trigger ratio, clock |

| 02,03         | 1 | Reads ranges selected and memory capacity on R1-R12                     |

| $2_{X},5_{X}$ | * | Reads data from selected channel on R1-12, and overflow on R13          |

| 80            | * | Test LAM FF                                                             |

| 90            |   | Arm module for a digitizing cycle                                       |

| 100           |   | Resets LAM FF                                                           |

| 160,161       | * | Sets active memory size, operating mode, pre/post trigger ratio, clock  |

| 170           | * | Sets module to read mode, presets address counter                       |

| 240           |   | Disables LAM response                                                   |

| 250           | * | Trigger cycle                                                           |

| 251           | * | Stops cycle                                                             |

| 252           | 1 | Abort cycle                                                             |

| 260           |   | Enables LAM response                                                    |

| 270           | * | Tests LAM FF                                                            |

| Z(S2)         |   | Resets module                                                           |

| X             |   | All valid commands generates X=1                                        |

| L             |   | An L is generated if the LAM FF is set and the response is enabled.     |

CONNECTORS: Control Inputs LEMO RA00250, signal inputs RA0302

TEMPERATURE RANGE: 0°C to 50°C

INDICATORS: "N" module addressed

"ACTIVE" module active

"LAM" cycle complete

POWER: + 6v @ 800ma; + 24v @ 145ma; -24v @ 155ma

SIZE: #1 CAMAC module

#### **MODEL TR612/3**

The JOERGER ENTERPRISES, INC. MODEL TR612/3 is a six channel, 12 bit transient recorder. It is available with two memory sizes per channel 128K and 512K. Its maximum clock speed is 3MHZ with a 50% duty cycle. To insure this a 12MHZ crystal oscillator is used internally. This provides the correct duty cycle for 3MHZ, 2MHZ, 1MHZ and 100KHZ operation. Optional clock speeds of 3MHZ, 2MHZ, 1.5MHZ and 1MHZ are available. This 50% duty cycle is also required for the external clock at 3MHZ. See the Front Panel Signals section for complete clock input requirements. To achieve this 3MHZ performance and low power operation, the latest Analog Devices pipeline converter was used. This provides a S/H amplifier and on board voltage reference for the ADC. Either the internal crystal oscillator or an external clock can be selected to operate the module. The module is completely programmable. The active memory size, operating mode, pre/post trigger ratio, clock source and operating speed are loaded with commands F16(A0) and F16(A1). There are two modes of operation, normal or burst mode. The burst mode is selected with a one on W4, F16(A1). If W4 is not set the operating mode is set to normal. The normal mode features pre/post triggering. This is set in one eighth segments of the active memory chosen with data on W1-3, F16(A0). All 0's sets the mode for no pretrigger data. This is the post trigger mode. W4-6, F16(A0) sets the active memory size. As an example with W4, 5 and 6 set to one, the active memory would equal the total memory of 128K. With W4, 5, and 6 set to zero the active memory would be set to 16K. The clock source is set with W3, F16(A1) W3 selects the clock source, "0" uses the internal clock, "1" selects the front panel Clock In.

To verify the modules setup it can be read out with F0(A0) and F0(A1). In addition to the setup F0(A1), R7&8 will indicate whether the module is armed or active.

It should be remembered that for best performance any unused inputs should have their signal and return lines shorted together or terminated in 50 ohms. Each input is on a LEMO RA0302 connector. This has been done to isolate the channels and reduce crosstalk. Each channel also has its power and ground completely filtered from the other channels to reduce interference.

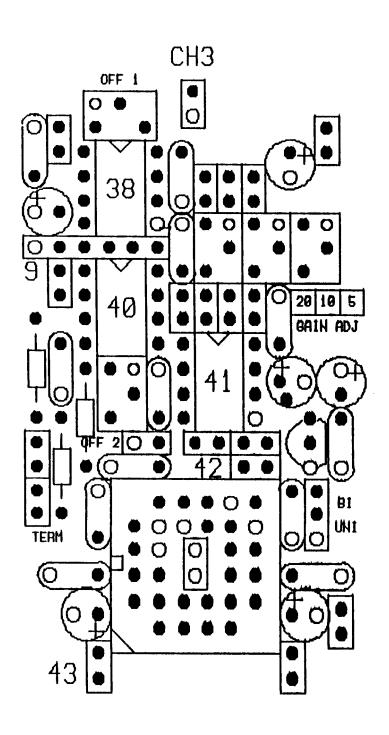

#### **AMPLIFIER SECTION**

To make maximum use of the 3MHZ clocking capability of the ADC a wide band amplifier section is incorporated. It has a minimum full scale band width of over 5MHZ, offers selectable input options of  $\pm 10$ v,  $\pm 5$ v,  $\pm 2.5$ v 0 to  $\pm 10$ v and 0 to  $\pm 5$  volts and both gain and offset adjustments are available. The input signal and return are buffered by a pair of high speed, unity gain amplifiers. The output of these amplifiers are summed in a differential amplifier with a set of four matched resistors. An offset adjustment is provided to insure a zero offset voltage from this section. The signal is then attenuated to handle the input range selected. A gain adjustment is provided for each range. The offset is also adjustable to handle the offset of the amplifier and the input of the ADC which is selectable for unipolar and bipolar operation. The module is shipped with the range set to  $\pm 5$  volts input although other ranges can be set and should be specified when ordering. The module will meet all its specifications but where improved accuracy for a selected input range is desired that range can be trimmed.

To further insure channel isolation and noise immunity each channel is completely filtered, both the amplifier and ADC sections. Filters are included on each channels power lines and the analog ground. This technique has proved invaluable on our other multichannel recorders and improved performance considerably.

To provide the user with the ability to identify the input range for each channel a set of three jumpers are provided for each channel. Two for gain and one for unipolar or bipolar operation. To insure this ability it means besides setting the actual amplifier range jumpers, these jumpers should also be set. Complete instructions are provided for their settings.

#### **OPERATION - NORMAL MODE**

The module is set up as always using commands F16(A0), and F16(A1) to set the operating conditions. If F16(A1) W4 is set to zero the module is set for normal mode. The "LAM" response is enabled with F26(A0). The module is armed with command F9(A0). If in a pretrigger mode the module will begin taking data. In any mode upon receipt of a trigger, either with command F25(A0) or a positive going TTL signal on the external trigger input, the post trigger cycle is started. Once the post trigger samples that have been preset have been taken the module will set an "L" and stop. This indicates the cycle is complete and the data can be read out. The readout sequence is started with F17(A0). This presets the readout counter with the address of the first data word stored internally. Readout is accomplished in a block transfer Q stop mode using command F2 or "FASTCAMAC" read F5 and the subaddress of the channel to be read. A Q = 0 will be returned to indicate that all the data recorded has been read out. To read another channel an F17 is again performed to preset the memory location and F2's or F5's with another subaddress are performed. Channels may be read or reread as needed.

#### "FASTCAMAC" READ

To increase data readout speed the module has implemented the FASTCAMAC, LEVEL 1 protocol in addition to F2 read. Command F5 with the appropriate subaddress initiates the fast read mode. The normal CAMAC cycle timing is used until the first S1 pulse. The controller reads data at the leading edge of S1. When the recorder receives the S1 pulse its leading edge clocks the address register to bring up the next data word. To meet the timing specifications the data must be valid at least 20 nsec before the leading edge of S1 and remain for a minimum of 10 nsec after S1's leading edge. To insure this timing a higher speed PLD has been used. The module is capable of the highest speed specified for Level 1, an S1 pulse of 200 nsec and a 200 nsec spacing. This 400 nsec period allows data to be continuously read at a rate of 2.5MHZ per word. Level 1 uses a standard CAMAC crate and standard open collector drivers. This means that the recorder is CAMAC compatible, will operate with other standard modules in the same crate and operate all the same commands it previously performed. The FASTCAMAC read is an additional feature to be used if high speed readout is desired. Upon receipt of the last S1 which indicates the recorder memory is completely readout a Q=0 is returned to the controller. With the next S1 the controller will sense Q=0, S2 will be generated and the FASTCAMAC read cycle will end.

#### **BURST MODE**

The module is set up, the LAM response enabled and the operating mode is set with F16(A1) W4=1. Now the active memory size becomes the burst size. The burst mode only uses all post trigger samples and so data set on W1-3 is ignored. The memory size used in the burst mode is the full memory size of the channel (128k or 512k). Command F9(A0) again arms the module but it does not begin taking data. Data recording is initiated by a trigger from either F25(A0) or an external trigger signal. When a trigger is received a burst of samples is taken equal in length to the active memory size and digitizing stops, but the module is still active. Now each trigger loads another burst of samples. When the total memory is full, an "L" is set indicating the memory is full, active is reset and no more triggers will be accepted.

Readout is again started with command F17(A0) and then F2's or F5's with the subaddress of the channel to be read. Q = 0 will be returned when the channels memory is completely read out, in this mode the total memory of the channel

Data is read out one channel at a time on R1-12 with an out of range bit on R13. The out of range bit and data can be used to sense either underrange or overrange. Data is presented in straight binary for unipolar ranges and offset binary for bipolar ranges.

**NOTE**: All post cycles or burst cycles can be shortened by stopping synchronously using the front panel stop or F25(A1) or by aborting the cycle using F25(A2). Data will still be valid using F17A0 then F2(Ax) or F5(Ax) as in a normal readout. except that the Q=0 response will not indicate when new data ends due to the unprogrammed stop. The Clock Out signal can be counted (up edge) to keep track of the number of samples taken.

Bursts may also be controlled manually from the front panel or the dataway allowing multiple bursts with variable sample sizes. This uses multiple Trigger/Stop inputs or multiple F25(A0) / F25(A1) commands or a combination of these signals. Set up for this is F16(A0) W4-6=1 and F16(A1) W4=1 (add clock source and speed as needed). After arming with F9(A0), multiple Trigger/Stops will be accepted until the memory is full, then the module will be disarmed. To keep track of burst sizes or trigger points the clock output can be used since it is the memory address counter clock (up edge). This will be useful in finding the trigger points in the data after readout. To readout data before the memory is full use abort, F25(A2), before readout.. Readout is done normally using F17(A0) to preset readout address and F2(Ax) or F5(Ax) to read data.

#### FRONT PANEL INDICATORS

"N" Red LED flashes for approximately 50ms or duration of N when module is addressed

"ACTIVE" Green LED lights when module is digitizing

"LAM" Red LED lights when LAM FF is set

#### FRONT PANEL SIGNALS

#### One pin LEMO connectors - RA 00250

CLOCK OUT The actual digitizing clock, up edge active. Not a continuous clock.

CLOCK IN The external clock source which can be selected as the digitizing clock using

Register 2. The clock input must meet or exceed a minimum pulse width both high and low of 167ns. This translates to a 50% duty cycle for a clock in of 3MHZ. Lower rate clocks may deviate from a 50% duty cycle as long as the minimum

pulse widths are satisfied.

TRIGGER External trigger (or'ed with F25A0) will synchronously start post trigger portion of

digitizing cycles. Module must be armed (pretrigger setups) or active (all posttrigger setups) to accept internal trigger. In normal modes the digitizing cycle will stop when the selected posttrigger size has been filled with samples. In burst mode the number of posttrigger samples taken for each trigger is the size of the selected active memory and the cycle will stop when the entire channel memory is

full.

STOP IN External stop (or'ed with F25A1) will synchronously stop a normal digitizing cycle

short of its programmed size, disarming module or synchronously stop a posttrigger segment in burst mode without disarming. In burst mode this allows multiple Trigger/Stop inputs to control the size of each posttrigger record and

digitizing will stop when the total memory is filled.

STOP OUT Directly connected to Stop In.

#### Two pin LEMO connectors - RA 0302

INPUT 1 Analog input CH1, readout using subaddress A0 INPUT 2 Analog input CH2, readout using subaddress A2 INPUT 3 Analog input CH3, readout using subaddress A3 INPUT 4 Analog input CH4, readout using subaddress A4 INPUT 5 Analog input CH5, readout using subaddress A5 INPUT 6 Analog input CH6, readout using subaddress A6

NOTE: Signal on pin 2 (bare pin), Return on pin 1 (shrouded socket)

# TR612/3 COMMAND SUMMARY

|             | COMMAND DESCRIPTION                                                                                                                                                               |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F0A0        | Read Register 1; pre/post and active memory sizes (see tables)                                                                                                                    |

| F0A1        | Read Register 2; frequency and source, mode, armed, active (see tables)                                                                                                           |

| F0A2        |                                                                                                                                                                                   |

| <del></del> | Read the range for channels 1-4 (see tables)                                                                                                                                      |

| F0A3        | Read the range for channels 5-6 and the total memory per channel (see tables)                                                                                                     |

| F2Ax/       | Read digitized samples from channel (x + 1) in block transfer Q stop mode. Data is                                                                                                |

| F5Ax        | read out one channel at a time on R1-12 with the LSB on R1, MSB on R12 and an out                                                                                                 |

| (x=0-5)     | of range bit on R13. The out of range bit and data can be used to sense either                                                                                                    |

|             | underrange or overrange. As an option data can be read out 2 channels at a time on                                                                                                |

|             | R1-24, with no out of range bit. (This must be specified with order.) Data format is                                                                                              |

|             | straight binary for unipolar ranges and offset binary for bipolar ranges. The readout                                                                                             |

|             | must first be enabled with F17A0. Then issue F2Ax's or F5Ax's until Q=0 (with all zero                                                                                            |

|             | data) is returned to complete the readout of the active memory for the selected channel.                                                                                          |

|             | Samples are readout oldest sample first for all modes. For pre/post modes the trigger                                                                                             |

|             | point can be located by using the setup information. Readout is only available when                                                                                               |

|             | the module is not armed or active. To read a different channel (even if previous                                                                                                  |

|             | channel readout is not completed), use F17A0 again and then F2Ax or F5Ax with the                                                                                                 |

| :           | new subaddress. The first valid F2Ax will reset the LAM FF. A reset *, F25A2 (abort) or                                                                                           |

| F0.4.0      | F9A0 (arm) will disable the readout.                                                                                                                                              |

| F8A0        | Test L, Q = 1 if LAM FF is set and response is enabled (F26A0)                                                                                                                    |

| F9A0        | Arm the module for a digitizing cycle. It will reset the LAM FF and disable a readout if it                                                                                       |

|             | has not been completed. If the module is set for any pretrigger samples the module will                                                                                           |

|             | be set to active and the digitizer will start filling the memory with samples. Otherwise a                                                                                        |

| F10A0       | trigger is needed to set active and start digitizing.  Clear the LAM FF                                                                                                           |

| F16A0       |                                                                                                                                                                                   |

| F16A1       | Write Register 1; pre/post and active memory sizes (see tables)                                                                                                                   |

| F17A0       | Write Register 2; sample clock frequency and source, mode, active (see tables)                                                                                                    |

| 11770       | Enable readout, only if module is not armed or active. Sets memory address to oldest data location. Must be used before readout using F2Ax.                                       |

| F24A0       | Disable the LAM response on the dataway L line                                                                                                                                    |

| F25A0       | Internal trigger (or'ed with front panel Trigger) will supply short mark trigger                                                                                                  |

| 123/10      | Internal trigger (or'ed with front panel Trigger) will synchronously start post trigger portion of digitizing cycles. Module must be armed (pretrigger setups) or active (all     |

|             |                                                                                                                                                                                   |

|             | posttrigger setups) to accept internal trigger. In normal modes the digitizing cycle will stop when the selected posttrigger size has been filled with samples. In burst mode the |

|             | number of posttrigger samples taken for each trigger is the size of the selected active                                                                                           |

|             | memory and the cycle will stop when the entire channel memory is full.                                                                                                            |

| F25A1       | Internal stop (or'ed with front panel Stop) will synchronously stop a normal digitizing                                                                                           |

|             | cycle short of its programmed size disarming module or synchronously stop a                                                                                                       |

|             | posttrigger segment in burst mode without disarming. In burst mode this allows multiple                                                                                           |

|             | Trigger/Stop inputs to control the size of each posttrigger record and digitizing will stop                                                                                       |

|             | when the total memory is filled.                                                                                                                                                  |

| F25A2       | Abort any cycle; digitizing (disarms and resets all FF') or readout (disables). Not                                                                                               |

|             | synchronous. Does not change module setup registers.                                                                                                                              |

| F26A0       | Enable the LAM response on the dataway L line                                                                                                                                     |

| F27A0       | Test LAM FF Q=1 if LAM is set                                                                                                                                                     |

|             | et = Power up or 7S2                                                                                                                                                              |

<sup>\*</sup> reset = Power up or ZS2

TR612/3 X + Q RESPONSES

|       | Х | Q | COMMENTS                                                  |

|-------|---|---|-----------------------------------------------------------|

| F0A0  | 1 | 1 |                                                           |

| F0A1  | 1 | 1 |                                                           |

| F0A2  | 1 | 1 |                                                           |

| F0A3  | 1 | 1 |                                                           |

| F2Ax/ | 1 | * | Q=1 if readout has been enabled (F17A0) and then Q=0      |

| F5Ax  |   |   | after last sample for CH (x+1) is readout                 |

| F8A0  | 1 | * | Test L, Q=1 if LAM is set and response is enabled (F26A0) |

| F9A0  | 1 | + |                                                           |

| F10A0 | 1 | - |                                                           |

| F16A0 | 1 | * | Q=1 if module is not armed or active                      |

| F16A1 | 1 | * | Q=1 if module is not armed or active                      |

| F17A0 | 1 | * | Q=1 if module is not armed or active                      |

| F24A0 | 1 | - |                                                           |

| F25A0 | 1 | * | Q=1 if armed                                              |

| F25A1 | 1 | * | Q=1 if armed                                              |

| F25A2 | 1 | 1 |                                                           |

| F26A0 | 1 | - |                                                           |

| F27A0 | 1 | * | Test LAM FF Q=1 if LAM is set                             |

LAM is set on end of active (normal mode posttrigger size done, burst mode all memory done) Power up or ZS2 resets registers and aborts any cycle

#### **REGISTER 1 - PRE/POST SIZE / ACTIVE MEMORY SIZE**

F16(A0), WRITE REG, (6 B ITS); F0(A0), READ REG, (6 BITS)

|       |     | , , , , , , , , , , , , , , , , , , , , | ,                 |

|-------|-----|-----------------------------------------|-------------------|

| W1/R1 | 1   | PRE/POST SIZE BIT 1                     |                   |

| W2/R2 | 2   | PRE/POST SIZE BIT 2                     | CODED 0-7         |

| W3/R3 | 4   | PRE/POST SIZE BIT 3                     |                   |

| W4/R4 | 8   | ACTIVE MEM SIZE BIT 1                   |                   |

| W5/R5 | 16  | ACTIVE MEM SIZE BIT 2                   | CODED 0-7         |

| W6/R6 | 32  | ACTIVE MEM SIZE BIT 3                   |                   |

| W7/R7 | 64  | NOT USED                                | READ RETURNS ZERO |

| W7/R8 | 128 | NOT USED                                | READ RETURNS ZERO |

## PRE/POST SAMPLE SIZE CODING - Eight's of the selected active memory

| CODE VALUE | PRE TRIGGER SIZE | POST TRIGGER SIZE |

|------------|------------------|-------------------|

| 0          | 0/8              | 8/8               |

| 1          | 1/8              | 7/8               |

| 2          | 2/8              | 6/8               |

| 3          | 3/8              | 5/8               |

| 4          | 4/8              | 4/8               |

| 5          | 5/8              | 3/8               |

| 6          | 6/8              | 2/8               |

| 7          | 7/8              | 1/8               |

all post trigger samples

# ACTIVE MEMORY SIZE CODING (Burst size when in Burst mode)

| CODE VALUE | 128k R/ | AM / CH | 512k RAM / ( | CH (OPTION) |

|------------|---------|---------|--------------|-------------|

| 0          | 1/8     | 16k     | 1/8          | 64k         |

| 1          | 2/8     | 32k     | 2/8          | 128k        |

| 2          | 3/8     | 48k     | 3/8          | 192k        |

| 3          | 4/8     | 64k     | 4/8          | 256k        |

| 4          | 5/8     | 80k     | 5/8          | 320k        |

| 5          | 6/8     | 96k     | 6/8          | 384k        |

| 6          | 7/8     | 112k    | 7/8          | 448k        |

| 7          | 8/8     | 128k    | 8/8          | 512k        |

## **REGISTER 2 - FREQUENCY / MODE**

F16(A1), WRITE FREQ (3 BITS), MODE (1 BIT); F0(A1), READ REG (6 BITS)

| W1/R1 | 1   | FREQ, BIT 1                                        | SAMPLE RATE       |

|-------|-----|----------------------------------------------------|-------------------|

| W2/R2 | 2   | FREQ, BIT 2                                        | CODED 0-4         |

| W3/R3 | 4   | 0 = INT CLOCK<br>1 = EXT CLOCK                     | (BIT SIGNIFICANT) |

| W4/R4 | 8   | 0 = NORMAL MODE<br>1 = BURST MODE                  | (BIT SIGNIFICANT) |

| W5/R5 | 16  | NOT USED                                           | READ RETURNS ZERO |

| W6/R6 | 32  | NOT USED                                           | READ RETURNS ZERO |

| R7    | 64  | 0 = TR612/3 IS NOT ARMED<br>1 = TR612/3 IS ARMED   | READ ONLY         |

| R8    | 128 | 0 = TR612/3 IS NOT ACTIVE<br>1 = TR612/3 IS ACTIVE | READ ONLY         |

#### SAMPLE RATE FREQUENCY CODING

| CODE VALUE | FOR I | NT CLOCK | FOR EXT CLOCK | OPTION/ | AL CLOCK |

|------------|-------|----------|---------------|---------|----------|

| 0          | 333ns | 3MHZ     | EXT CLOCK / 2 | 333ns   | 3MHZ     |

| 1          | 500ns | 2MHZ     | EXT CLOCK / 2 | 500ns   | 2MHZ     |

| 2          | 1.0us | 1MHZ     | EXT CLOCK / 2 | 667ns   | 1.5MHZ   |

| 3          | 10us  | 100KHZ   | EXT CLOCK / 2 | 1000ns  | 1MHZ     |

#### **RANGE READOUT TABLE**

F0(A2), READ RANGE SETTINGS FOR CHANNELS 1 TO 4

| CH1               | CH2               | CH3               | CH4                 | RANGE                                         |

|-------------------|-------------------|-------------------|---------------------|-----------------------------------------------|

| R1                | R4                | R7                | R10                 | 0 = UNIPOLAR<br>1 = BIPOLAR                   |

| R2<br>R3<br>coded | R5<br>R6<br>coded | R8<br>R9<br>coded | R11<br>R12<br>coded | 0 = 5V<br>1 = 10V<br>2 = 20V*<br>3 = not used |

<sup>\*</sup>BIPOLAR ONLY

F0(A3), READ RANGE SETTINGS FOR CHANNELS 5 and 6 and MODULE MEMORY CAPACITY (per channel)

| CH5               | CH6               | RANGE                                        |

|-------------------|-------------------|----------------------------------------------|

| R1                | R4                | 0 = UNIPOLAR<br>1 = BIPOLAR                  |

| R2<br>R3<br>coded | R5<br>R6<br>coded | 0 = 5V<br>1 =10V<br>2 = 20V*<br>3 = not used |

<sup>\*</sup>BIPOLAR ONLY

|     | MEMORY SIZE   |

|-----|---------------|

| R12 | 0 = 128K / CH |

| 1   | 1 = 512K / CH |

# ANALOG FRONT END RANGE JUMPERS AND ADJUSTMENT LOCATIONS (CH1 as example, all other channels are similar) ALSO SET RANGE READOUT JUMPERS TO MATCH

|           |    |    | <b>JUMPERS</b> |    |          |

|-----------|----|----|----------------|----|----------|

| RANGE     | 20 | 10 | 6              | BI | UNI      |

| ±2.5v     |    |    | IN             | IN |          |

| ±5v       |    | IN |                | IN |          |

| ±10v      | IN |    |                | IN | <u> </u> |

| 0 to +5V  |    |    | IN             |    | IN       |

| 0 to +10v |    | IN |                |    | IN       |

Shipped In ±5v range

RANGE READOUT JUMPERS SET RANGE TO MATCH ANALOG FRONT END JUMP

| SEI KANGE | SEI KANGE IO MAICH ANALOG FRONT END JUMPERS   | ALOG FRONT  | END JUMPERS |

|-----------|-----------------------------------------------|-------------|-------------|

|           |                                               | JUMPERS     |             |

| RANGE     | γy                                            | 8x          | Cx          |

| ±2.5v     | Z                                             |             |             |

| ×Ç∓       | Z                                             | N           |             |

| ±10v      | Z                                             |             | Z           |

| 0 ta +5V  |                                               |             |             |

| 0 ta +10v |                                               | Z           |             |

| x=1706    | x = 1  TO  6 for CHANNELS 1 TO 6 RESPECTIVELY | S 1 TO 6 RE | SPECTIVELY  |

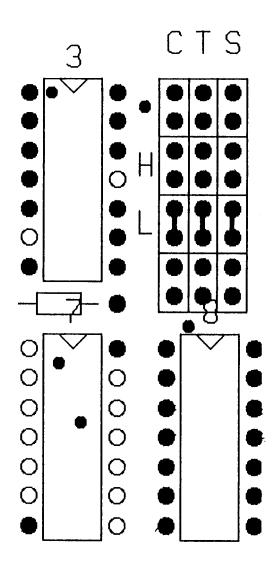

# FRONT PANEL INPUT POLARITY JUMPERS

C = CLOCK IN

T = TRIGGER

S = STOP IN

H = INPUT PULLED UP WITH 10K OHMS TO +5V; THE UP EDGE IS THE ACTIVE EDGE

L = INPUT IS TERMINATED WITH 500 OHMS TO GROUND; THE UP EDGE IS THE ACTIVE EDGE

Shipped with all "L" jumpers in.

#### WARRANTY

ALL EQUIPMENT MANUFACTURED BY JOERGER ENTERPRISES, INC. IS WARRANTED AGAINST DEFECTS IN MATERIAL AND WORKMANSHIP FOR A PERIOD OF ONE YEAR FROM THE DATE OF SHIPMENT. JOERGER ENTERPRISES, INC. WILL REPAIR OR REPLACE, AT THEIR OPTION, ANY EQUIPMENT DEFECTS FOUND IN WORKMANSHIP OR MATERIAL. THIS WARRANTY IS APPLICABLE TO THE ORIGINAL PURCHASER AND ONLY COVERS EQUIPMENT JUDGED BY JOERGER ENTERPRISES, INC. TO HAVE RECEIVED NORMAL PROPER USE.

ALL REPAIRS WILL BE PERFORMED AT THE JOERGER ENTERPRISES, INC. FACTORY. NO EQUIPMENT WILL BE ACCEPTED FOR REPAIR WITHOUT PRIOR APPROVAL BY THE FACTORY. EQUIPMENT MUST BE RETURNED PREPAID. THE WARRANTY ON EQUIPMENT RETURNED FROM OUTSIDE THE CONTINENTAL USA IS LIMITED TO REPAIR OF THE EQUIPMENT AND DOES NOT COVER SHIPPING, CUSTOMS CLEARANCE OR ANY OTHER CHARGES.

ANY EQUIPMENT PURCHASED BY JOERGER ENTERPRISES, INC. FOR RESALE WILL CARRY ONLY THE ORIGINAL MANUFACTURERS WARRANTY.

EQUIPMENT THAT IS NO LONGER COVERED UNDER WARRANTY WILL BE REPAIRED AT COST. AN ESTIMATE OF THESE REPAIRS WILL BE SUBMITTED TO THE CUSTOMER AND AFTER RECEIVING HIS WRITTEN APPROVAL, REPAIRS WILL PROCEED.

JOERGER ENTERPRISES, INC. DOES NOT ASSUME OR AUTHORIZE ANY OTHER PERSONS OR REPRESENTATIVES TO ASSUME ANY OTHER LIABILITIES IN CONNECTION WITH THEIR EQUIPMENT.

EVERY EFFORT WILL BE MADE TO REPAIR DEFECTIVE EQUIPMENT AS SOON AS POSSIBLE. A CLEAR DESCRIPTION OF THE MALFUNCTION ACCOMPANIED WITH THE UNIT WILL SPEED THE TURN-AROUND TIME.