RIG OFFSET. RIT GAIN

Bi Ra SYSTEMS, INC. 2404 COMANCHE N.E. ALBUQUERQUE, N.M. 87107

TRANSIENT DIGITIZER TYPE 908 MODEL 5908

OPERATIONS MANUAL

# TABLE OF CONTENTS

|       | P                                  | age        |

|-------|------------------------------------|------------|

| 1.0   | PRELIMINARY                        | 1          |

| 1.1   | MEMORY LENGTH                      | 1          |

| 1.2   | NUMBER OF ACTIVE CHANNELS          | 1          |

| 1.3   | ANALOG INPUT LEVEL AND OUTPUT CODE | 1          |

| 1.4   | CLOCK SOURCE                       | 1          |

| 1.5   | MODE OF OPERATION                  | 1          |

| 2.0   | SWITCH SETTINGS                    | 1          |

| 2.1   | MEMORY LENGTH                      | 1          |

| 2.2   | ADC VOLTAGE INPUT RANGES           | 3          |

| 3.0   | OUTPUT CODING STRAPS               | 3          |

| 4.0   | INPUT REQUIREMENT                  | 4          |

| 4.1   | ANALOG                             | 4          |

| 4.2   | CLOCK                              | 4          |

| 4.3   | TRIGGER                            | 4          |

| 4.4   | BASE FREQUENCY FOR INTERNAL CLOCK  | 4          |

| 5.0   | PLACING THE 908 IN OPERATION       | 5          |

| 5.1   | INSTALLATION IN THE CRATE(S)       | 5          |

| 6.0   | CALIBRATION PROCEDURE              | <b>'</b> 5 |

| 6.1   | EQUIPMENT                          | 5          |

| 6.2   | ANALOG CHANNEL CALIBRATION         | 5          |

| 6.2.1 | MODULE DISASSEMBLY                 | 5 &        |

| 6.3   | CALIBRATION VERIFICATION OF ADC    | 7          |

| 6.4   | SELF TEST ANALOG WAVEFORM          | 8          |

| 6.4.1 | OV TO 10V CALIBRATION              | Q & (      |

# TABLES & FIGURE

| TABLE  | 2.1   | MEMORY LENGTH SELECT                     |

|--------|-------|------------------------------------------|

| TABLE  | 2.2.1 | ADC INPUT RANGE SELECT SWITCHES          |

| TABLE  | 3.0   | OUTPUT CODING STRAPS                     |

| TABLE  | 4.4   | BASE FREQUENCY SELECT                    |

| FIGURE | 6.1   | TRANSIENT DIGITIZER DISPLAY BOARD        |

| TABLE  | 6.2.1 | MODEL 5903 ANALOG CHANNEL MONITOR POINTS |

| TABLE  | 6.4   | SELF TEST STRAPPING                      |

### Transient Digitizer Type 908 (Model 5908)

### Operations Manual

1:0 Preliminary

Prior to use of the module determine the following requirements.

1.1 Memory length

Model 5903 memory modules are directly compatible with the 5908. The 5903 contains 32K X 16 words in each module. Up to 1 meg word of memory in multiples of 32K may be used. All signal communication between the 5903 and 5908 occurs via the rear auxillary connector whose mate is a Viking 3VH18 or equivalent. The back plane of the crate employed shall incorporate the interconnect requirements of the 5903 and 5908 units. Memory length is switch selectable via the 903.

1.2 Number of active channels

Active channels are dataway selectable and may be 4, 8, 16, 32. See Commands F16AO.

1.3 Analog Input level and output code

Input range is switch selectable for:

+2.56 Volts +5.12 Volts 0 to +5.12 Volts 0 to +10.24 Volts

Coding may be unipolar binary, offset binary, or two's complement by MSB strap.

#### 1.4 Clock source

The source is dataway selectable for either internal or external clock. External clock is opto-coupled, terminated in approx. 50 n, and requires a current of 10ma to be active. Minumum external clock period is determined by the formula (No. of Active channels X 5µsec.) + 5µs. Internal clock period should be equal to or greater than the that of the external clock for the active channels employed.

1.5 Mode of Operation

Mode is dataway controlled for either PRETRIGGER or POSTTRIGGER operation. For the Pre-trigger mode, the number of POST-TRIGGER samples must be determined prior to initation of the sequence. See commands F16AO.

2.0 Switch Settings

All switches are accessible via cutouts of the left PC board outside cover.

2.1 Memory length

The DIP switch is located at the upper front of the card. Individual switches are numbered in sequence fron left to right beginning with the number 1. Select required memory length from table.

2.1.1 Schematic reference designation is SW3 on Drawing number 5908-D-001 sheet 2 Left Board.

Table 2.1 Memory Length Select

|   | Swi | tch |     |   |                | Memory     | Number of          |

|---|-----|-----|-----|---|----------------|------------|--------------------|

| 1 | 2   | 3   | 4   | 5 | 6              | Length "K" | 944 Modules<br>908 |

| X | 0   | 0   | 0   | 0 | 0              | 32         | 1                  |

| X | 0   | 0   | 0   | 0 | 1              | 64         | 2                  |

| X | 0   | 0   | 0   | 1 | 0              | 96         | 3                  |

| х | 0   | 0   | 0   | 1 | 1              | 128        | 4                  |

| X | 0   | 0   | · 1 | 0 | 0              | 160        | 5                  |

| X | 0   | 0   | 1   | 0 | 1              | 192        | 6                  |

| X | 0   | 0   | 1   | 1 | O <sub>.</sub> | 224        | 7                  |

| x | 0   | 0   | 1   | 1 | 1              | 256        | 8                  |

| x | 0   | 1   | 0   | 0 | 0              | 288        | 9                  |

| X | 0   | 1   | 0   | 0 | 1              | 320<br>:   | 10                 |

| x | 0   | 1   | 1   | 1 | 1              | 512        | 16                 |

| X | 1   | 0   | 0   | 0 | 0              | 544        | 17                 |

| X | 1   | 1   | 0   | 0 | 0              | 800        | 25                 |

| Х | 1   | 1:  | 1   | 1 | 1              | 1024       | 32                 |

1 = OFF, 0 = ON, X = Don't Care

### 2.2 ADC Voltage Input Ranges

Analog input level is controlled by two DIP switches located near the center lower edge of the left board. The rear switch has 2 rockers with positions C1 & C2, C3 & C4 and the front switch has 1 rocker with positions C1 & C2. The schematic designations are SWi-A, SW-1B (2 rockers) and SW2. Switch settings for corresponding input levels are as indicated in Table 2.2.1. Listed C1, C2, C3, C4 for the appropriate switch indicates the DOWN position of the rockers. When range is changed, Paragraph 6.3, calibration verification of ADC should be performed.

Table 2.2.1 ADC Input Range Select Switches

| INPUTS       | SW    | ITCH NO.   |     |

|--------------|-------|------------|-----|

| Volts        | SW1-A | SW1-B      | SW2 |

| 0 to 10.24   | C1    | <b>c</b> 3 | C2  |

| 0  to  +5.12 | C1    | C4         | C1  |

| + 5.12       | C2    | С3         | C2  |

| ÷ 2.56       | C2    | CŢ.        | C1  |

#### 3.0 Output Coding Straps

Output coding is determined by the strapping of the ADC MSB. Codes are Unipolar Binary, Offset Binary and Two's Complement. Princeton TFTR-10C6-H908 Para 6.6.8 specifies the data output coding for transfer on to the dataway read lines. Therefore, the coded data into the memory for unipolar 0 to +10.24V and ±5.12 Volt shall be as listed in Table 3.0.

Three wire wrap terminals are provided to connect the output to the ADC MSB or NOT MSB output. The terminals are at the upper right corner of the ADC cutout on the left PC board. Upper, middle and lower pins are the Output, MSB and NOT MSB respectively. Units are shipped from the factory strapped for unipolar, O to +10.24V full scale. If a different range is selected, the ADC offset and gain should be verified as defined in the calibration procedure.

Table 3.0 Output Coding Straps

| Voltage Input               | CODE             | St             | rap Term     | inals       |

|-----------------------------|------------------|----------------|--------------|-------------|

| Range                       | •                | Upper (output) | Middle (MSB) | Lower (MSB) |

| 0 to +10.24V<br>0 to +5.12V | Unipolar Binary  | X              | Х            | open        |

| + 5.12V<br>+ 2.56V          | Two's Complement | X              | open         | X           |

### 4.0 Input Requirements

All input signals except the internal oscillator (and dataway 1MHz for generation of internal clock) are via LEMO 3 pin Model RG.OB.303. Mates are FG.OB.303. Connectors are mounted with keyway up. Viewed from front of the module, and beginning with Keyway going clockwise, pins are: 1 (shield), 2 (positive), and 3 (negative).

### 4.1 Analog

Analog inputs are provided on front panel, labeled 1 through 32. Inputs are 10K ohm ±1 percent balanced to ground. Inputs are overvoltage protected via 5.1K limiting resistors. Signal plus common mode cannot exceed ±17.5V for proper operation. In all modes of operation channels are scanned beginning with channel 1 through the last selected channel. Unused inputs may be left open.

### 4.2 Clock

Two paralleled front panel connectors are provided and connect to the isolated inputs of a 10MHz opto-coupler. Clock is active on the leading edge of the positive input current transition and limited by approximately 50 ohm series resistor. Normal ON current is 10ma (5V); off current of zero (approx. 1.2V).

External clock period cannot exceed the time specified by the following equation:

Period can be equal to, or less than (number of selected chan. multiplied by 5 microsec.) + 5usec.

| The | maximum | frequency | for | selected | channels | is | as | shown: |

|-----|---------|-----------|-----|----------|----------|----|----|--------|

|-----|---------|-----------|-----|----------|----------|----|----|--------|

| SELECTED<br>CHANNELS | MICROSEC<br>PERIOD | MAX FREQ.<br>KHz |  |  |

|----------------------|--------------------|------------------|--|--|

|                      |                    |                  |  |  |

| 4                    | 25                 | 40.00            |  |  |

| 8                    | 45                 | 22,22            |  |  |

| 16                   | 85                 | 11.76            |  |  |

| 32                   | 165                | 6.06             |  |  |

### 4.3 Trigger

Trigger input specifications are the same as the clock. A single pulse is required for proper operation after each Dataway ARM.

# 4.4 Base Frequency for Internal Clock

Three Strap points are provided for selection of the 1MHz source to generate the internal clock. Units are factory strapped to use the 5908 1 MHz clock but may be altered in the field.

Strap terminals are located on the center board directly in front of the top edge of the dataway connector. The module must be partially disassembled to alter straps. Terminal functions and labels are as listed:

Table 4.4 Base Frequency Select

| Strap point | Function             |

|-------------|----------------------|

| E1          | Dataway signal out   |

| E2          | Internal Clock Input |

| E3          | Internal Oscillator  |

Strap E1 to E2 for use of dataway 1MHz Strap E2 to E3 for use of 1MHz internal oscillator.

### 5.0 Placing the 908 in Operation

WARNING: DO NOT INSERT OR REMOVE MODULES FROM CAMAC CRATE WITH POWER ON OR DAMAGE TO THE MODULE MAY RESULT.

The crate(s) employed shall be equiped with an AUXILLARY BUSS BOARD, Bi Ra Model 5900. The 5900 interconnects the model 5903 with the model 5908 memory modules when installed in the crate. Crates are interconnected using a Bi Ra Model 5901 EXPANSION CABLE.

## 5.1 Installation in the Crate(s).

Insert the 5908 and 5903 memories in the crate(s). If memories are in more than one crate use a Model 5901 to interconnect the 5900 boards.

Connect analog input cables, trigger, and clock as required. The 5908 can now be controlled by CAMAC commands via a user generated program employing commands listed in technical manual.

### 6.0 Calibration Procedure

Calibration should be checked anytime the user finds the Analog sections are not within the specifications of the Technical manual or verified when the ADC range is changed (see Para 2.2) or every 180 days.

### 6.1 Equipment

- 1 Oscilloscope, 10V, 1MHz, calibrated gain

- 1 DC Calibration source 0 to ±10.24V, Analogic Model AN3100 or equiv.

- 1 DVM Fluke 8100A or equivalent

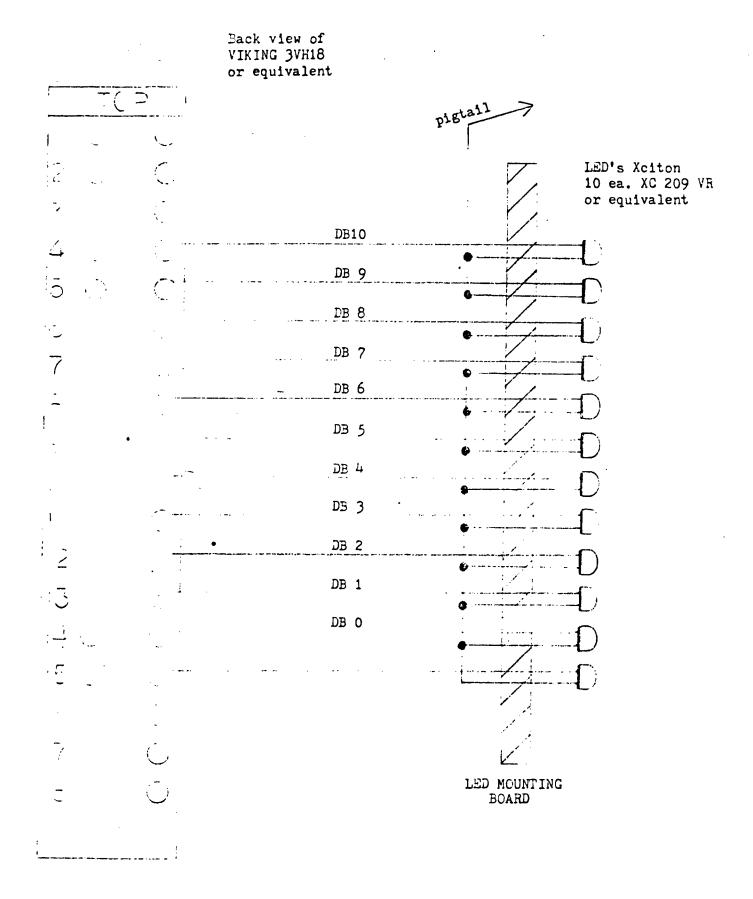

- 1 Display board (Auxillary connector) see Fig. 6.1

- 3 Extender Cards Bi Ra 8201-2 or equivalent

- 1 CAMAC Powered Crate

- 1 Potiometer adjusting screw driver

- 1 Pulser capable of 0 to +5V, 10ma peak pulse, rep. rate 0-10 cps

- 2 Adapter cables with LEMO FG.OB.303 connector at one end.

#### 6.2 Analog Channel Calibration

All 32 analog channels contain identical, low drift, very stable components. Only offset adjustments are required for the SHM-1C-1 Sample and Hold circuits.

Access to the Center and Right PC board multiplexers HI516 is required to monitor the voltage of each channel output during the "Follow" mode of the respective sample and Hold circuits.

## 6.2.1 Module Disassembly

- 1. Remove all front and rear panels to rail mounting screws except the Right board front panel.

- 2. Remove rear panel and carefully pull back panel enough for clearance of the board mounted LED's.

- 3. Fan out the PC board for access to the Right and Center PC board HI516 multiplexers U20 and U24 respectively. Use care to not disconnect interconnect cables.

- 4. Turn CRATE POWER OFF and install the three 8201-2 Extenders in adjacent Crate slots. Connect LEFT, CENTER, and RIGHT boards of 5903 to respective LEFT, RIGHT, CENTER extenders.

- 5. Turn Crate Power ON All 5903 LED's shall be OUT. If not, issue Z + C to clear. Allow approximately 5 minutes for temperature stabilization.

- 6. Start with the center board HI516 (U24). Connect DVM ground to grounded end of R83 (end closest to U24). With DVM probe tip monitor the voltage at each of the U24 inputs listed in Table 6.2.1.

FIGURE 6.1 TRANIENT DIGITIZER DISFLAY BOARD

First apply zero volts to Channel 1 front panel input and adjust R65 for 0.0000 Volts on DVM at U24-19. Then apply +10.24V and -5.12V. Verify Voltage gain is within ±02%. Repeat for the remaining Channels.

NOTE: Center board zero adjustment pots are in two rows accessible at the top and bottom of the card. The outer row of the top edge beginning from the front are R65, R66, R67, R68. Inner row beginning with front is R69, R70, R71, R72. Lower outer row beginning with fourth from front POT is R73, R74, R75, R76. Inside row beginning from FRONT is R77, R78, R79, R80.

The RIGHT Board pot lay out is identical with the center except the RIGHT board has two additional pots not associated with the Channel Zero Adjust.

Table 6.2.1 Model 5903 Analog Channel Monitor Points

|       | Center Board | i         |       | Right Board |           |

|-------|--------------|-----------|-------|-------------|-----------|

| Chan. | U24          | Zero Adj. | Chan. | U24         | Zero Adj. |

| No.   | pin No.      | R No.     | No.   | pin No.     | R No.     |

| 1     | 19           | 65        | 17    | 19          | 65        |

| 2     | 20           | 66        | 18    | 20          | 66        |

| 3     | 21           | 67        | 19    | 21          | 67        |

| 4     | 22           | 68        | 20    | 22          | 68        |

| 5     | 23           | 69        | 21    | 23          | 69        |

| 6     | 24           | 70        | 22    | 24          | 70        |

| 7     | 25           | 71        | 23    | 25          | 71        |

| 8     | 26           | 72        | 24    | 26          | 72        |

| 9     | 11           | 73        | 25    | 11          | 73        |

| 10    | 10           | 74        | 26    | 10          | 74        |

| 11.   | 9            | 75        | 27    | 9           | 75        |

| 12    | 8            | 76        | 28    | 8           | 76        |

| 13    | 7            | 77        | 29    | 7           | 77        |

| 14    | 6            | 78        | 30    | 6           | 78        |

| 15    | 5            | 79        | 31    | 5           | 79        |

| 16    | 4            | 80        | 32    | 4           | 80        |

Ground Point for DVM Center - grounded end of R83 Right - Pin 12 of U20

# 6.3 Calibration Verification of ADC

- 1. CAMAC Crate OFF, install the 5903 in the Model 8201-2 extenders, and insert the extenders into three adjacent slots to be occupied by the 5908. Mount display board on 5903 auxillary connector so lights are visible. Lay the 5903 on its right side for address to the bottom edge of the left Card.

- 2. Connect Pulser output to one of the front panel CLOCK connectors so that pin 2 and 3 are positive and negative respectively.

- 3. Apply CAMAC Crate Power. Issue a CAMAC Z + C followed by a single F16AO with dataway write line input to select.

- a. Pre-trigger mode W1 = 1

- b. External clock W2-c. Four (4) Active Channels W2 - W5 = 0

- W6. W7 = 1

- d. One Post-trigger Sample Count W9 = 1, W10-W24 = 0

- The 5908 "N" LED will flash for F16AO. "ARM" and "ACT" lights will remain lighted. Allow approximately 5 minutes for analog circuit stabilization.

- 5. display will update for each positive pulse input at the CLOCK input. Indication should be within one count of zero input for the respective Setting of the ADC tinput Range Select Switches. See Paragraph 2.2 and Table 2.2.1.

- 6. Connect the remaining LEMO adapter cable to the 5908 front panel connector labeled 4(Channel 4 input). Set AN3100 calibrator Voltage output OFF and connect calibrator positive, negative output to Channel 4 lemo pins 2, 3 respectively. Set calibrator dials for zero output voltage and apply AC power.

- 7. Verify LED display reading. For unipolar setting adjust OFF-SET (second from dataway on top side of left board) for a 50% dither between digital 000 - 01 and 000 - 00. Right digit is LSB.

NOTE: LED lamps are on for Digital 0. OFF for 1. LSB = DBO LED.

For Bipolar set input voltage from calibrator to MINUS Full Scale plus 1 LSB and adjust OFFSET for 50% dither between codes 000 - - - 01 and 000 - - - 00.

Note MSB is shown for BIPOLAR, NOT Two's complement. MSB for 2's Comp. will be digitial 1 (OFF) GAIN ADJ are made for both configurations with input levels set to PLUS FULL SCALE MINUS 1 LSB. Adjust GAIN (Pot back of OFFSET ADJ) for 50% dither between 111 - - 10 and 111 - - 11.

- 8. Remove all external inputs from 5903 front panel. Turn CAMAC Crate Power OFF. Remove Extenders from Crate and 5903 from extender.

- 9. Repeat Paragraph 5.1 to install 5903 into Crate.

### 6.4 Self Test Analog Waveform

The waveform is traingular with a repetition rate of about 200Hz. A preamplifier provides a full scale adjust via R88 followed by a post amplifier with strap points A, B, C, D, and an off-set to provide a signal compatible with the ADC range selected if so desired. Units are shipped from the factory with a strap and gain setting to provide a O(-0+50mV) to 10V (+0-50mV) waveform. To verify accuracy monitor strap point to ground with oscilloscope. See Table 6.4 for strapping. Circuit is located on the RIGHT PC board.

Table 6.4 Self Test Strapping

| Post Amp     | Strap points |        |  |

|--------------|--------------|--------|--|

| Gain         | Strap        | Open   |  |

| 2            | A to B       | C to D |  |

| 1            | NONE         | ALL    |  |

| <del>1</del> | C to D       | A to B |  |

Strap and monitor points are accessible through RIGHT PC board outside panel cut-outs. Module must be place on extenders to calibrate. Use care when strapping is changed so that wire particles will not get inside unit and cause malfunction. Strap for gain of 2. Strap terminals beginning with A located at rear of lower slot cut; B is front of cutout. Upper cutout contains D (rear) and C.

# 6.4.1 OV to 10V calibration

- 1. With Power off of Crate, Install 8201-2 extenders in crate and to the 5903. Lay 5903 on left side.

- 2. With scope tip monitor terminal B and adjust R88 (GAIN) pot. (POT is nearest rear of right PC board outer bottom row). Set close to 5.0V peak to peak. Disregard any offset.

- 3. With scope monitor strap point D and adjust R88 for as near 10V peak to peak signal as possible.

4. Connect DVM between strap point D and ground and adjust R81 (offset) pot. (Pot is at outer edge of RIGHT board nearest rear of unit). Set for +5.000 volts. Resulting waveform should be 0 to 10V with tolerance of 0 + 50 mV.

NOTE: If Self Test signal is to be compatible with unipolar 0 to +5.12, strap gain of  $\frac{1}{2}$  adjust OFFSET for +2.56 Volts, Bipolar +5.12V, Strap post amp gain for 1 and adjust OFFSET fro OVDC. For +2.56 F.S. STRAP gain for  $\frac{1}{2}$  with offset at zero. Output signals will be 0 to +5V, -5V to +5V and, -2.5 to +2.5 respectively.