## MODEL 162 BOXCAR AVERAGER

INCLUDING:

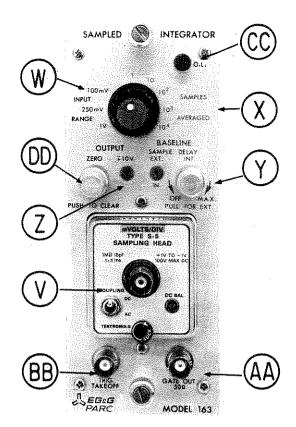

MODEL 163

SAMPLED INTEGRATOR

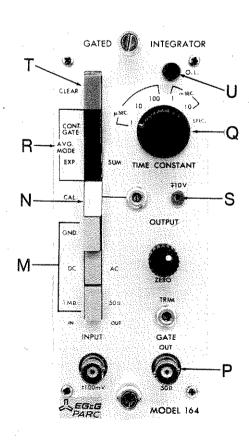

MODEL 164

GATED INTEGRATOR

READ SAFETY NOTICE PRECEDING SECTION I BEFORE OPERATING INSTRUMENT

**OPERATING AND SERVICE MANUAL**

## MODEL 162 BOXCAR AVERAGER

INCLUDING:

MODEL 163

SAMPLED INTEGRATOR

MODEL 164

GATED INTEGRATOR

**OPERATING AND SERVICE MANUAL**

JEGEG PRINCETON APPLIED RESEARCH

#### SHOULD YOUR EQUIPMENT REQUIRE SERVICE

- A. Contact the factory (609/452-2111) or your local factory representative to discuss the problem. In many cases it will be possible to expedite servicing by localizing the problem to a particular plug-in circuit board.

- B. If it is necessary to send any equipment back to the factory, we need the following information.

- Model number and serial number.

- (2) Your name (instrument user).

- (3) Your address.

- (4) Address to which instrument should be returned.

- (5) Your telephone number and extension.

- (6) Symptoms (in detail, including control settings).

- (7) Your purchase order number for repair charges (does not apply to repairs in warranty).

- (8) Shipping instructions (if you wish to authorize shipment by any method other than normal surface transportation).

- U.S. CUSTOMERS—Ship the equipment being returned to:

EG&G PRINCETON APPLIED RESEARCH 7 Roszel Road (Off Alexander Road, East of Route 1) Princeton, New Jersey

- D. CUSTOMERS OUTSIDE OF U.S.A.—To avoid delay in customs clearance of equipment being returned, please contact the factory or the nearest factory distributor for complete shipping information.

- E. Address correspondence to:

EG&G PRINCETON APPLIED RESEARCH P. O. Box 2565 Princeton, NJ 08540

Phone: 609/452-2111 TELEX: 84 3409

#### WARRANTY

EG&G PRINCETON APPLIED RESEARCH warrants each instrument of its manufacture to be free from defects in material and workmanship. Obligations under this Warranty shall be limited to replacing, repairing or giving credit for the purchase price, at our option, of any instrument returned, freight prepaid, to our factory within ONE year of delivery to the original purchaser, provided prior authorization for such return has been given by our authorized representative.

This Warranty shall not apply to any instrument which our inspection shall disclose to our satisfaction, has become defective or unworkable due to abuse, mishandling, misuse, accident, alteration, negligence, improper installation or other causes beyond our control. Instruments manufactured by others, and included in or supplied with our equipment, are not covered by this Warranty but carry the original manufacturer's warranty which is extended to our customers and may be more restrictive. Certain subassemblies, accessories or components may be specifically excluded from this Warranty, in which case such exclusions are listed in the Instruction Manual supplied with each instrument.

We reserve the right to make changes in design at any time without incurring any obligation to install same on units previously purchased.

THERE ARE NO WARRANTIES WHICH EXTEND BEYOND THE DESCRIPTION HEREIN. THIS WARRANTY IS IN LIEU OF, AND EXCLUDES ANY AND ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESSED, IMPLIED OR STATUTORY, INCLUDING MERCHANTABILITY AND FITNESS, AS WELL AS ANY AND ALL OTHER OBLIGATIONS OR LIABILITIES OF EG&G PRINCETON APPLIED RESEARCH, INCLUDING, BUT NOT LIMITED TO, SPECIAL OR CONSEQUENTIAL DAMAGES. NO PERSON, FIRM OR CORPORATION IS AUTHORIZED TO ASSUME FOR EG&G PRINCETON APPLIED RESEARCH ANY ADDITIONAL OBLIGATION OR LIABILITY NOT EXPRESSLY PROVIDED FOR HEREIN EXCEPT IN WRITING DULY EXECUTED BY AN OFFICER OF EG&G PRINCETON APPLIED RESEARCH.

### **TABLE OF CONTENTS**

| Section | 1                                | Pa                                                  | age   |  |

|---------|----------------------------------|-----------------------------------------------------|-------|--|

| 1       | CONDENSED OPERATING INSTRUCTIONS |                                                     |       |  |

| II      | CHARA                            | ACTERISTICS                                         | 11 4  |  |

|         | 2.1                              | Introduction                                        |       |  |

|         | 2.2                              | Description                                         |       |  |

|         | 2.2                              |                                                     |       |  |

|         |                                  |                                                     |       |  |

|         | 2.3                              |                                                     |       |  |

|         | 2.3                              | Applications                                        |       |  |

|         |                                  | 2.3A Picosecond Domain Fluorescence Studies         | 11-4  |  |

|         |                                  | 2.3B Fluorescence and Phosphorescence Decay Studies |       |  |

|         |                                  | 2.3C Pulsed Ultrasonics                             |       |  |

|         |                                  | 2.3D Pulsed Resonance Experiments                   |       |  |

|         |                                  | 2.3E Laser Development                              |       |  |

|         |                                  | 2.3F Optical Absorption Studies                     | 11-4  |  |

|         |                                  | 2.3G Sampling Scope.                                |       |  |

|         |                                  | 2.3H Other Applications                             |       |  |

|         | 2.4                              | Specifications                                      | 11-5  |  |

|         |                                  | 2.4A Model 162 Boxcar Averager (Mainframe)          |       |  |

|         |                                  | 2.4B Model 163 Sampled Integrator                   | 11-7  |  |

|         |                                  | 2.4C Model 164 Gated Integrator                     | 11-9  |  |

|         |                                  | 2.4D AccessoriesII                                  | 1-10  |  |

|         |                                  |                                                     |       |  |

|         | INITIAL                          | _ CHECKS                                            |       |  |

|         | 3.1                              | Introduction                                        | -1    |  |

|         | 3.2                              | Equipment Needed                                    | -1    |  |

|         | 3.3                              | Preliminary Steps                                   | 111-1 |  |

|         | 3.4                              | Procedure if Processor Module is Model 163          | 111-2 |  |

|         | 3.5                              | Procedure if Processor Module is Model 164          | III-3 |  |

|         |                                  | 3.5A Checks in the External Trigger Mode            |       |  |

|         |                                  | 3.5B Internal Trigger Mode Checks                   |       |  |

|         |                                  | 3.5C Hold Checks.                                   |       |  |

|         | 3.6                              | Dual-Channel Operation                              |       |  |

|         | *.*                              | / .                                                 | 0     |  |

| łV      | OPERA                            | ATING INSTRUCTIONS                                  | IV.1  |  |

| •       | 4.1                              | Introduction                                        |       |  |

|         | 4.2                              | Preliminary Considerations.                         |       |  |

|         | -7 · Æ                           | 4.2A Installation                                   |       |  |

|         |                                  | 4.2B Power Requirements.                            |       |  |

|         |                                  | 4.2C Fusing                                         |       |  |

|         |                                  | 4.2D Grounding                                      |       |  |

|         |                                  | 4.2E Cooling                                        |       |  |

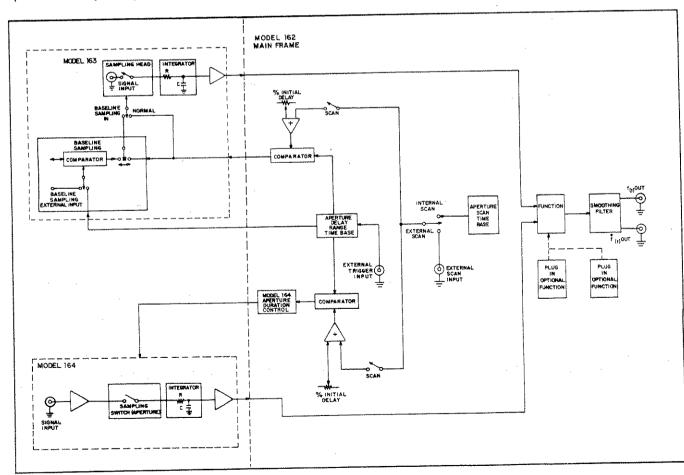

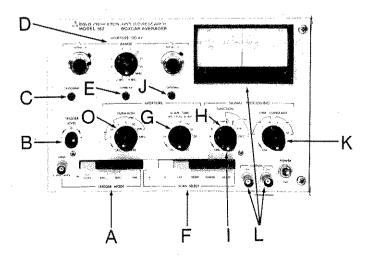

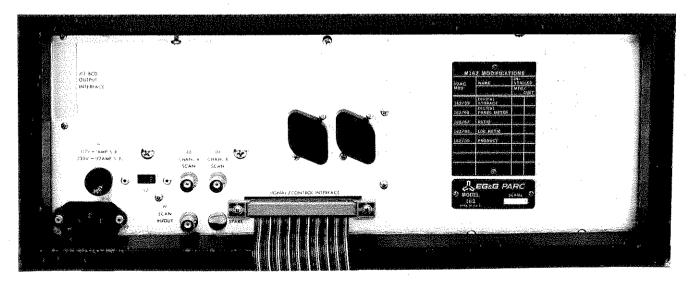

|         | 4.3                              | Controls, Connectors, and Indicator Lamps.          |       |  |

|         | 4.3                              |                                                     |       |  |

|         |                                  |                                                     | IV-1  |  |

|         |                                  |                                                     | IV-3  |  |

|         |                                  | 4.3C Model 164 Processor Module                     |       |  |

|         |                                  | 4.3D Rear Panel                                     |       |  |

| •       | 4.4                              | Detailed Operating Considerations, Introduction.    |       |  |

|         | 4.5                              | Synchronization                                     |       |  |

|         |                                  | 4.5A Introduction                                   |       |  |

|         |                                  | 4.5B External Trigger Mode                          |       |  |

|         |                                  | 4.5C Line Trigger Mode                              |       |  |

|         |                                  | 4.5D Internal Trigger Mode                          |       |  |

|         | 4.6                              | Input Signal Processing, General                    | IV-9  |  |

|     | 4.7   | Input Signal Processing, Model 164                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |       | 4.7A Input Impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |       | 4.76 Input Coupling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| *** |       | 4.70 GND Pushbutton                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |       | 4.7D CAL Pushbutton                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |       | 4.7E Zero Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |       | 4.7F EXP/SUM Pushbutton                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |       | 4.7G Cont. Gate Pushbutton                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |       | 4.7H Clear                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |       | 4.71 Time Constant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

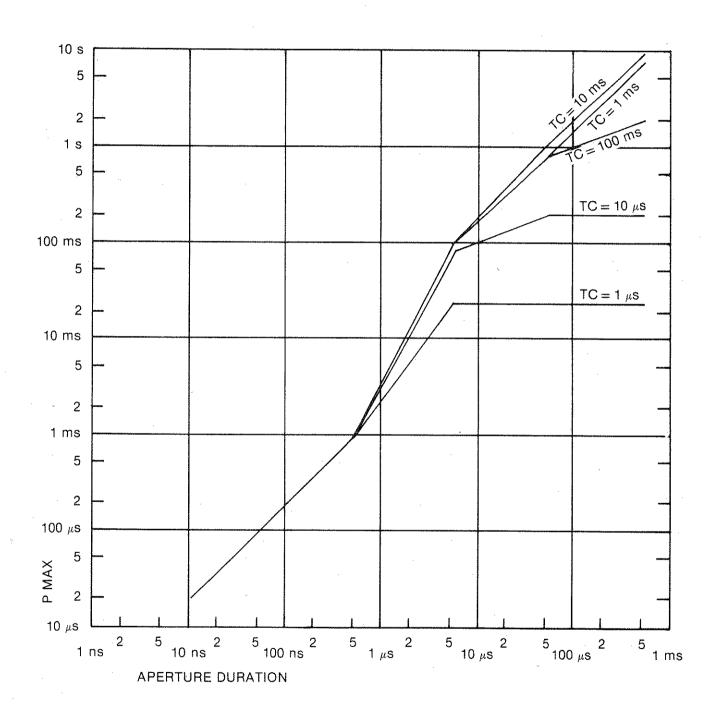

|     |       | 4.73 Aperture Duration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |       | 4.78 Dynamic Reserve                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     | 4.8   | input Signal Processing, Model 163                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |       | 4.0A input inipedance, Coupling, and Risetime.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |       | 4.0B DC Balance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |       | 4.00 Sensitivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     |       | 4.8D Dynamic Reserve                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |       | 4.0E Samples Averaged, SNIR, and Trigger Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |       | 4.8F Clear and Zero                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

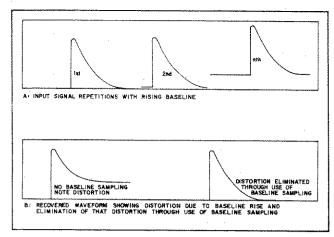

|     |       | 4.0G Baseline Sampling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |       | 4.011 Trigger Takeoff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     |       | 4.01 Odiput Fill Jack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

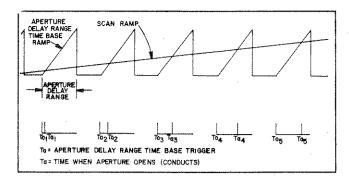

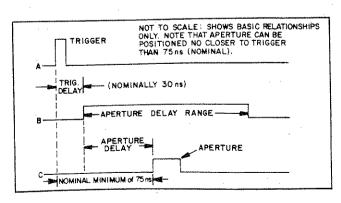

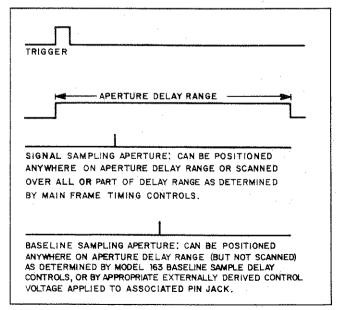

|     | 4.9   | Aperture Delay Hange                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     | 4.10  | Aperture PositionIV-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |       | 4.1UA SINGIE-POINT Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |       | 4.10B Scanned Analysis, Internal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     |       | 4.100 Scanned Analysis, External                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 4.11  | near-raner Scan Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

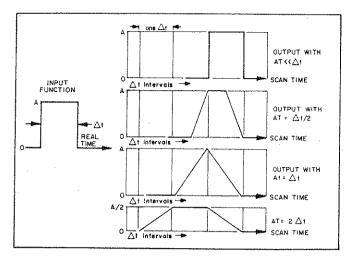

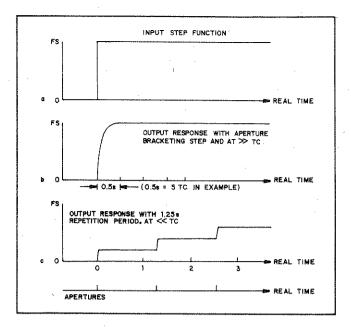

|     | 4.12  | Scall time and Resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |       | 4.12A introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |       | 4.12B Model 164                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |       | 4.12C Model 163                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |