# technical information manual

CAMAC Model 8100

Dual Programmable Differential Amplifier

# WARRANTY

All LRS instruments are guaranteed to operate within their specifications for one year from the date of purchase. Under this warranty, any unit which fails to perform within specifications, as a result of defects in workmanship or materials, will be restored to specified operating condition free of charge except for shipping costs involved in the return of the unit to the factory.

In order that this warranty be considered valid, it is necessary that the LRS Warranty Card which accompanies the unit on delivery be completed and returned to the factory within 30 days of receipt of equipment.

All questions concerning repairs or replacement parts should be addressed directly to factory's Quality Control Manager. This procedure will insure the fastest possible service. Please include the Model Type, Serial Number, and ECN (Engineering Change Number) with all requests for parts or service.

ENGINEERING DEPARTMENT LeCroy/CALIFORNIA PALO ALTO, CALIFORNIA

#### TABLE OF CONTENTS

Page Number

| Title | Page | and | Warranty |

|-------|------|-----|----------|

|-------|------|-----|----------|

| Page | and                  | warranty                                                                                                                                              |                                               |

|------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 1.   | Fron                 | t Panel Photograph and Description                                                                                                                    |                                               |

| 2.   | Spec                 | rifications                                                                                                                                           |                                               |

| 3.   | Oper                 | rational Description                                                                                                                                  | 1-1                                           |

|      | c.                   | General Front Panel Inputs, Controls, & Outputs CAMAC Interface To Set Amplifier Gain, To Ground Inputs, or To Switch Filter To Read Amplifier Offset | 1-1<br>1-1<br>1-3<br>1-4<br>1-5               |

| 4.   | f.                   | To Read Amplifier Gain, Filter, Grounding, and CAMAC Access Status                                                                                    | 1-5<br>2-1                                    |

| 3.   | a.<br>b.<br>c.<br>d. | General Input Attenuators First Amplifier Stage Interstage Attenuator 200KHZ Filter                                                                   | 2-1<br>2-2<br>2-2<br>2-3<br>2-3<br>2-3<br>2-4 |

- Drafting Symbols 5.

- Schematics 6.

# TECHNICAL DATA

# **CAMAC Model 8100**

# Dual Programmable Differential Amplifier

- Programmable input range—from .1 volt-50 volt full scale

- Good common mode rejection 40 db at 100 KHz

- Excellent frequency response—DC to 1 MHz

- Convenient cut-off filter-200 KHz

The LeCroy Model 8100 Programmable Differential Amplifier is designed to provide signal conditioning and noise immunity for experiments where gain has to be optimized quickly and flexibly to extend the dynamic range of the following instrumentation. The gain of the amplifier is fully programmable by computer through international standard CAMAC interface. On the other hand, all settings can be made by hand to facilitate setup in the absence of a computer.

The single-ended outputs are designed to match the line of CAMAC transient recorders offered by LeCroy for research in fusion and other areas. The outputs can drive a high impedance to  $\pm 10$  volt or a 50 ohm impedance to  $\pm \frac{1}{2}$  volt. The differential inputs are accommodated by a shielded 2 element LEMO connector and can operate in presence of a common signal of up to 100 volt. A switch selectable cut-off filter is available to limit the 1 MHz band width to 200 KHz in order to prevent aliasing when in use with the LeCroy Model 8210 or Model 2264 transient recorders (typical sampling rates of 1 MHz). The common mode rejection is 100 to 1 at 100 KHz on the 100 mV range, is better at lower frequencies and higher gain setting, and is worse at high frequencies and lower gains.

The Model 8100 is packaged in a number 1 width CAMAC module to permit front-panel, switch-selectable-gain knobs and is the first in an expanding line of signal conditioning circuits being designed for use with waveform digitizers in experiments studying transient phenomena.

Preliminary: January 1979

Instrumentation for the study of transient phenomena

# PRELIMINARY SPECIFICATION **CAMAC MODEL 8100 Dual Programmable Differential Amplifier**

#### Input Characteristics

Type: Differential Amplifier, shielded 2 element LEMO connectors

Impedance: 1 M ohm, 30 pf

Input Ranges: 9 steps from 0.1 to 50V in a 1, 2, 5 sequence. Local settable by 2 three position switches for .1, 1, and 10 volts with a

multiplier of 1, 2, and 5. Programmable by computer in the same steps. Each channel can be independently set.

Common Mode Range: ±5V on .1, .2, .5V ranges ±50V on 1, 2, 5V ranges ±100V on 10, 20, 50V ranges

Common Mode Rejection: 100: 1 at 100 KHz on .1V range. 60db at 60 Hz on 10V range

Input Protection: 200V for 10µsec on all scales Frequency Response: DC to 500 KHz (1 db)

Anti aliasing filter: Switch selectable 2 pole butterworth filter with 200 KHz cutoff (3db point). Switch selects filters for both amplifiers

at once; mpu interface can select filter on each amplifier separately.

#### **OUTPUT CHARACTERISTICS**

Maximum linear range:  $\pm 10V$  into high impedance ( $\pm .5V$  into  $50\Omega$ )

Output offset temperature coeff: 5mV/°C (1.0mV/°C optional at higher cost)

Output Impedance: 50Ω.

#### **GENERAL**

Gain: Settable for each channel in steps of .2 to 100 in a 1, 2, 5 sequence. See input range. Gains should be divided by 2 when driving  $50\Omega$ .

Input Offset Voltage: Computer settable by on-board DAC (offset binary code). Front Panel Toggle switch to set offset driving the DAC with up/down counter so that offset is readable and reproducible when switching from local to remote. DAC

resolution is approx. 2.7 mV/Step referred to the output. DAC range is  $\pm 5.5$ V (12 binary bits).

#### CONTROL AND READOUT FUNCTION:

**CAMAC Commands:** Q: A Q=1 response is generated only in recognition of a F(1)•N or F(0)•N when a valid word is being read. X: An X=1 (Command Accepted) response is generated when a valid F, N and A are generated.

CAMAC Code: F(0) A(0) reads channel 1 gain.

F(16)•A(0) sets channel 1 gain at S2. F(1)•A(0) reads channel 1 offset. F(17)•A(0) sets channel 1 offset at S2. F(0)•A(1) reads channel 2 gain. F(16)•A(1) sets channel 2 gain at S2. F(1)•A(1) reads channel 2 offset. F(17)•A(1) sets channel 2 offset at S2.

The A1-A8 lines are used to address the desired amplifier circuit. A(0) addresses amplifier #1 (upper amplifier), A(1) addresses amplifier #2 (lower amplifier).

F(0) reads gain and status information on the addressed amplifier. Status can be read whether or not the unit is in remote mode. Gain status is read on bits 1–6; bit 7 indicates status of amplifier ground setting, bit 8 indicates status of filter switch. When amplifier 1 is addressed, bit 9 indicates status of remote/local switch.

F(16) sets gain of the addressed amplifier. Bits 1-6 set amplifier gain, bit 7 can ground inputs, bit 8 switches the filter in or out.

F(1) reads the setting of the offset DAC on the addressed amplifier. Setting is offset binary, and data appears on the R1-R12 lines, with R1 the LSB and R12 the MSB. DAC setting can be read whether or not the unit is in remote mode.

F(17) sets the offset DAC on the addressed amplifier. Offset data is accepted on lines W1–W12, with W1 the LSB and W12 the MSB. DAC Polarity: Programming all (1)'s into the offset DAC register will offset the amplifier's output by the maximum negative amount (approximately -5.5V), assuming no input signal.

Packaging: In conformance with the CAMAC standard for nuclear modules (USAEC Reports TID-25875, IEE St. #583, ESONE Report 4100e) in an RF shielded #1 CAMAC package.

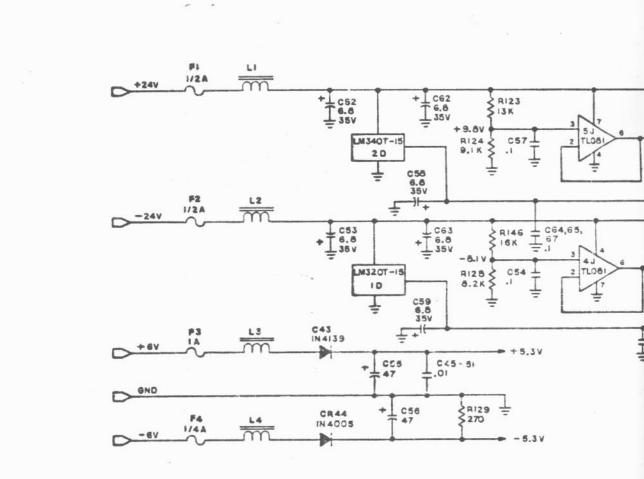

Current Requirements: +6V, 420mA; -6V, 20 mA; +24V, 140mA; -24V, 130mA.

| Switch selects the source of the Control Commands for both Amplifiers. With the switch in "LOCAL" position, the Front panel switches control Amplifier functions; with the switch in "REMOTE" position, the Front panel controls are desabled and the CAMAC Interface provides the control.  Switched to the "IN" position, this switch causes a 200 KHZ, 2 pole Butterworth filters to be switched in line with both Amplifiers. |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Switch selects the source of the Control Commands for both Amplifiers. With the switch in "LOCAL"  position, the Front panel switches control Amplifier functions; with the switch in "REMOTE" position, the Front panel controls are desabled and the CAMAC Interface provides the control.  Switched to the "IN" position, this switch causes a 200 KHZ, 2 pole Butterworth filters to be switched                              |  |

| Switch selects the source of the Control Commands for both Amplifiers. With the switch in "LOCAL"  position, the Front panel switches control Amplifier functions; with the switch in "REMOTE" position, the Front panel controls are desabled and the CAMAC Interface provides the control.  Switched to the "IN" position, this switch causes a 200 KHZ, 2 pole Butterworth filters to be switched                              |  |

| position, the Front panel switches control Amplifier functions; with the switch in "REMOTE" position, the Front panel controls are desabled and the CAMAC Interface provides the control.  Switched to the "IN" position, this switch causes a 200 KHZ, 2 pole Butterworth filters to be switched                                                                                                                                 |  |

| functions; with the switch in "REMOTE" position, the Front panel controls are desabled and the CAMAC Interface provides the control.  Switched to the "IN" position, this switch causes a 200 KHZ, 2 pole Butterworth filters to be switched                                                                                                                                                                                      |  |

| CAMAC Interface provides the control.  Switched to the "IN" position, this switch causes a 200 KHZ, 2 pole Butterworth filters to be switched                                                                                                                                                                                                                                                                                     |  |

| Switched to the "IN" position, this switch causes a 200 KHZ, 2 pole Butterworth filters to be switched                                                                                                                                                                                                                                                                                                                            |  |

| a 200 KHZ, 2 pole Butterworth filters to be switched                                                                                                                                                                                                                                                                                                                                                                              |  |

| a 200 KHZ, 2 pole Butterworth filters to be switched                                                                                                                                                                                                                                                                                                                                                                              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| This switch selects Amplifier GRIMS of 1, 10, or                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 100 for Amplifier #1.                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| QUIPUT                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| This switch selects a Multiplier of 1, .5, or .2,                                                                                                                                                                                                                                                                                                                                                                                 |  |

| which is applied to the Gain switch setting of Amplifier 1 to determine the overall Gain of the Amplifier.                                                                                                                                                                                                                                                                                                                        |  |

| Ampiriter 1 to determine the overall sain of the impiriter.                                                                                                                                                                                                                                                                                                                                                                       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| This switch allows the Dial which controls the Offset to be counted up or down. Pressing the switch in                                                                                                                                                                                                                                                                                                                            |  |

| the "-" direction causes the Amplifier to become                                                                                                                                                                                                                                                                                                                                                                                  |  |

| more negative.                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| AMPLIFIER #1                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Differential Input-1 MEG OHM input impedance.                                                                                                                                                                                                                                                                                                                                                                                     |  |

| AMPLIFIER #1 OUTPUT                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| Impedance 50 Ohms.                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| AMPLIFIER #2 GAIN SWITCH                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| Same as Amplifier #1.                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| AMPLIFIER #2 MULTIPLIER SWITCH.                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Same as Amplifier #1.                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| AMPLIFIER #2 OFFSET SWITCH. Same as Amplif. #1.                                                                                                                                                                                                                                                                                                                                                                                   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| AMPLIFIER #2 DIFFERENTIAL INPUT. 1 MEG Ohm Input Impedance.                                                                                                                                                                                                                                                                                                                                                                       |  |

| AMPLIFIER #2 OUTPUT. Impedance 50 Ohms.                                                                                                                                                                                                                                                                                                                                                                                           |  |

ENGINEERING DEPARTMENT LeCroy/CALIFORNIA

PALO ALTO, CALIFORNIA

#### OPERATIONAL DESCRIPTION

GENERAL: The LeCroy 8100 dual programmable amplifier contains 2 separate precision differential-input amplifiers with gains adjustable in a 1-2-5 sequence from .2 to 100, with a differential input from 50 volts to 100 millivolts, respectively, and a 500 khz 1-db bandwidth at all settings. Both amplifiers exhibit excellent common-mode rejection and offer a wide common-mode input range. Gain is settable either by front panel switches or via CAMAC commands.

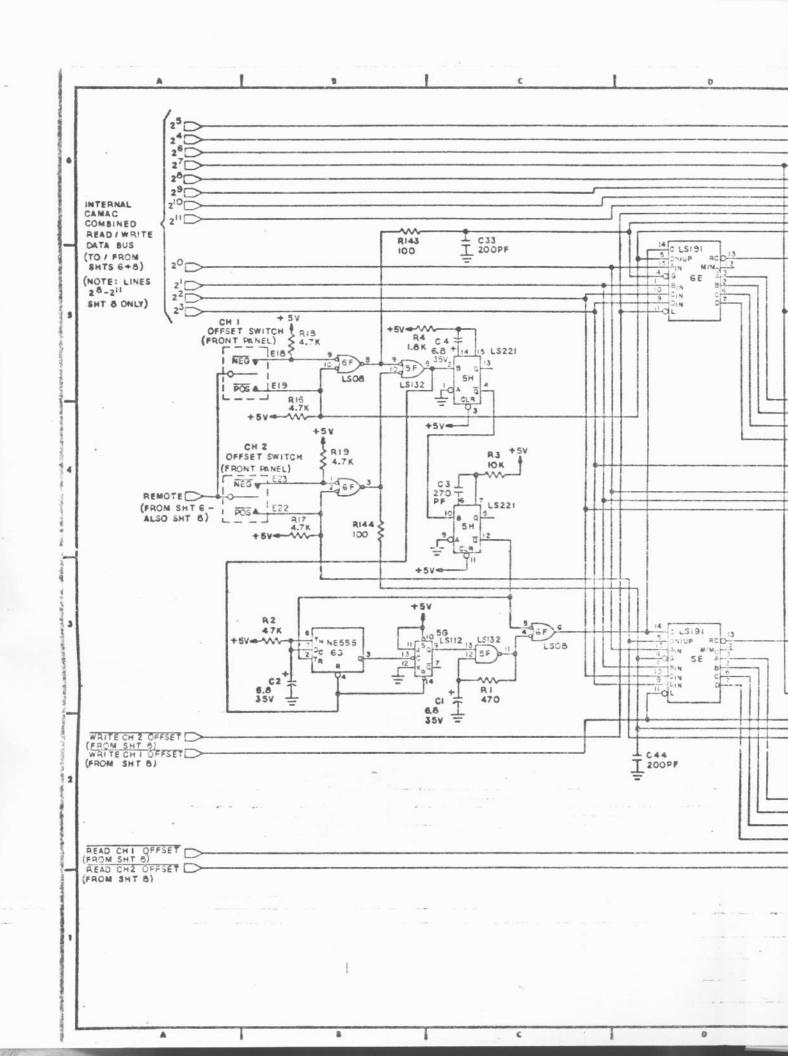

Each amplifier contains a switchable 200 khz, 2-pole Butterworth filter. A 12-bit D/A converter on each amplifier provides offset control with a range at the output of ±5.5 volts. The filters can be switched in or out together via a front panel switch, or can be independently switched by CAMAC commands. Complete status of the amplifier can be read at any time by the CAMAC interface.

# FRONT PANEL INPUTS, CONTROLS AND OUTPUTS

ANALOG INPUTS: Two differential Lemo connectors, one for each amplifier. Impedance at each input is 1 megohm to ground.

ANALOG OUTPUTS: Two single Lemo connectors, one for each amplifier.

Output impedance is 50 ohms. Output range into 1 kohm: + 10 volts;

into 50 ohms: + 2 volts max. Outputs will survive at least 5 seconds

of short circuit to ground.

REMOTE/LOCAL SWITCH: When this switch is in the Local position, the front panel switches control the amplifier characteristics; however, the CAMAC interface can still read the amplifier status.

When the switch is in the Remote position, all other front panel switches are disabled, and the amplifier charactersitics can be both set and read by CAMAC command. When the switch is changed from Local to Remote, however, all amplifier conditions that exist at the time are retained until the CAMAC interface commands a change, i.e. the amplifiers do not go into an undefined state.

When the switch is changed from Remote to Local, however, the amplifier characteristics revert to that which is indicated by the fromt panel switch positions, with the exception of the D/A setting, which remains as it was at the time of the change. If any amplifier inputs have been grounded by CAMAC command, they will be ungrounded when the switch is changed from Remote to Local.

FILTER SWITCH: When this switch is in the In position, a 200 khz (3db point) filter is switched in line with each amplifier. With the switch in the Out position, each amplifier reverts to its 500khz 1-db bandwidth.

GAIN AND MULTIPLIER SWITCHES: Each amplifier's gain is set by the combination of the Gain and Multiplier switches. The position of the Gain switch is multiplied by the setting of the Multiplier switch, e.g. if the Gain switch for amplifier 1 is set at 100, and amplifier

1's multiplier switch is set to .2, then the amplifier's overall gain is 20.

OFFSET SWITCHES: The offset switches each control a counter connected to the offset DAC in the amplifier associated with the switch. The switches are spring loaded to return to a center position. Pushing the switch momentarily to the left causes one count to be entered\_into the counter, such that the associated amplifer's output becomes approximately 2.7 mv more negative. A momentary push to the right causes the amplifier's output to become more positive by the same amount. If the switch is held either to the left or the right for more than 1 second, a continuous clock is switched into the negative or positive, respectively, until the switch is released. The speed of increase or decrease is such that the entire range of the DAC is traversed in approximately \_\_\_\_\_ seconds. If the lower or upper limit of the DAC is reached and passed while the switch is held in one of the active positions, the offset will simply switch to the opposite extreme and continue counting in the same direction until the switch is released.

#### CAMAC INTERFACE

In the following discussions, CAMAC nomenclature will be used, i.e. a "one" is defined as a TTL low level on the back connector.

TO SET AMPLIFIER OFFSET:

Amplifier #1: (Upper Amplifier) N.F(1-).A(0)(S2.W1--W12)

Amplifier #2: (Lower Amplifier) N.F(17).A(1)(S2.W1--W12)

1-4

Data is accepted on write lines W1--W12; the DAC is offset binary coded using W1 as the LSB and W12 as the MSB. Behavior of the amplifiers to different DAC settings is shown in the examples below:

W1 W2 W3 W4 W5 W6 W7 W8 W9 W10 W11 W12

- 2. Amplifier offset maximum

3. Amplifier offset near midrange:

0 0 0 0 0 0 0 0 0 0 0

TO SET AMPLIFIER GAIN, TO GROUND INPUTS, OR TO SWITCH FILTER:

Amplifier #1 (Upper Amplifier): N.F(16).A(0).S2.(W1-W8)

Amplifier #2 (Lower Amplifier): N.F(16).A(1).S2.(W1-W8)

| Write line/Switch position equivalents: | G   | AIN  |    | MU  | JLT. | -   | GND. | FILTER |

|-----------------------------------------|-----|------|----|-----|------|-----|------|--------|

|                                         | 100 | 10   | 1  | 1   | .5   | , 2 |      |        |

| Examples:                               | wl  | .M:3 | W3 | W-4 | W5   | W6  | W7   | W8     |

| 1.) Gain = 100, no filter ungrounded    | . 1 | 0    | 0  | 1   | 0    | 0   | 0    | 0      |

| 2.) Gain = 5, no filter, ungrounded     | . 0 | 1    | 0  | 0   | 1    | 0   | 0    | 0      |

| 3.) Gain = .2, no filter, ungrounded    | . 0 | 0    | 1  | 0   | 0    | 1   | 0    | 0      |

| 4.) Gain = 20, filtered, ungrounded     | . 1 | 0    | 0  | 0   | 1    | Ó   | 0    | 1      |

| 5.) Inputs grounded                     | . 0 | 0    | 0  | 1   | 0    | 0   | 1    | Х      |

LeCroy/CALIFORNIA

PALO ALTO, CALIFORNIA

Note that when the inputs are grounded, none of the lines in the gain group (W1-W3) are asserted. This effectively disconnects the amplifier from the input connector, so that the grounding switch is not working against any signal that may be connected there. Signals at the input connector in this situation will still see a 1 megohm inpedance to ground. It should also be noted that, when the inputs are grounded, one line of the Multiplier group should be asserted. If this is not done, the amplifier output will saturate.

Note also that in none of the examples is more than one line in the Gain group (W1-W3) or the Multiplier group (W4-W6) asserted. Doing so will not cause any damage to the amplifier, but will result in improper gain settings, changes in input impedance, or nonlinearity in response.

#### TO READ AMPLIFIER OFFSET

Amplifier #1 (Upper Amplifier): N.F(1).A(0).(R1-R2)

Amplifier #2 (Lower Amplifier): N.F(1).A(1).(R1-R12)

Data on the R lines has the same polarity and logic as is used to set the offset on the W lines.

TO READ AMPLIFIER GAIN, FILTER, GROUNDING, AND CAMAC ACCESS STATUS

Amplifier #1 (Upper Amplifier): N.F(0).A(0).(R1-R9)

Data on the R lines (R1-R8) has the same polarity and logic as is used

1-6

to set the gain, filter, and grounding on the W lines. R9 is used (when reading amplifier #1 status only) to indicate status of the Local/Remote switch: it is 1 if the unit is in Local mode.

Amplifier #2 (Lower Amplifier): N.F(0).A(1).(R1-R8)

Data on the R lines has the same polarity and logic as is used to set the gain, filter, and grounding on the W lines.

#### FUNCTIONAL DESCRIPTION

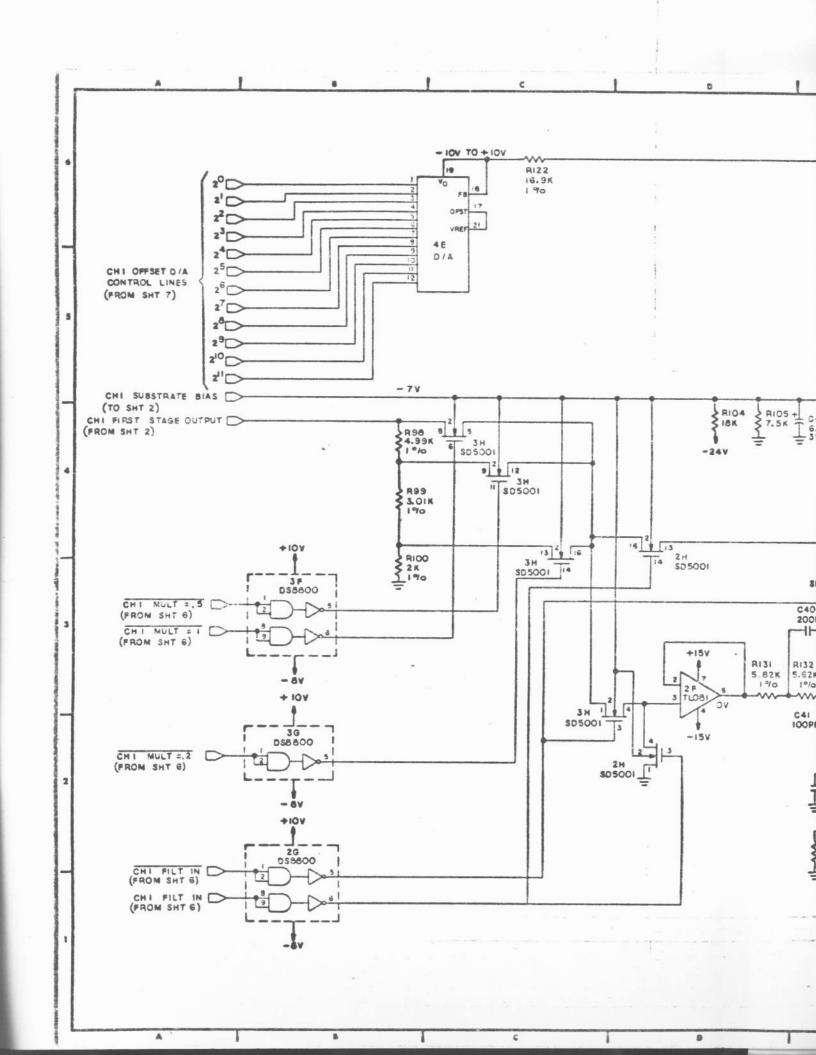

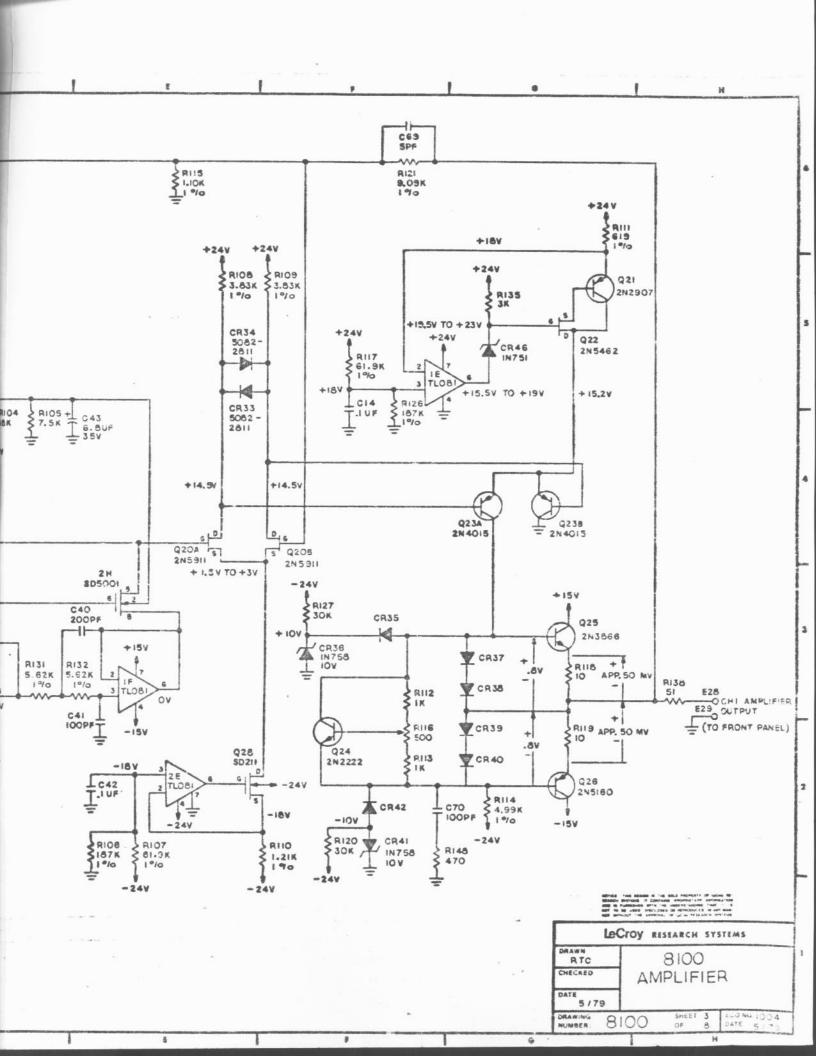

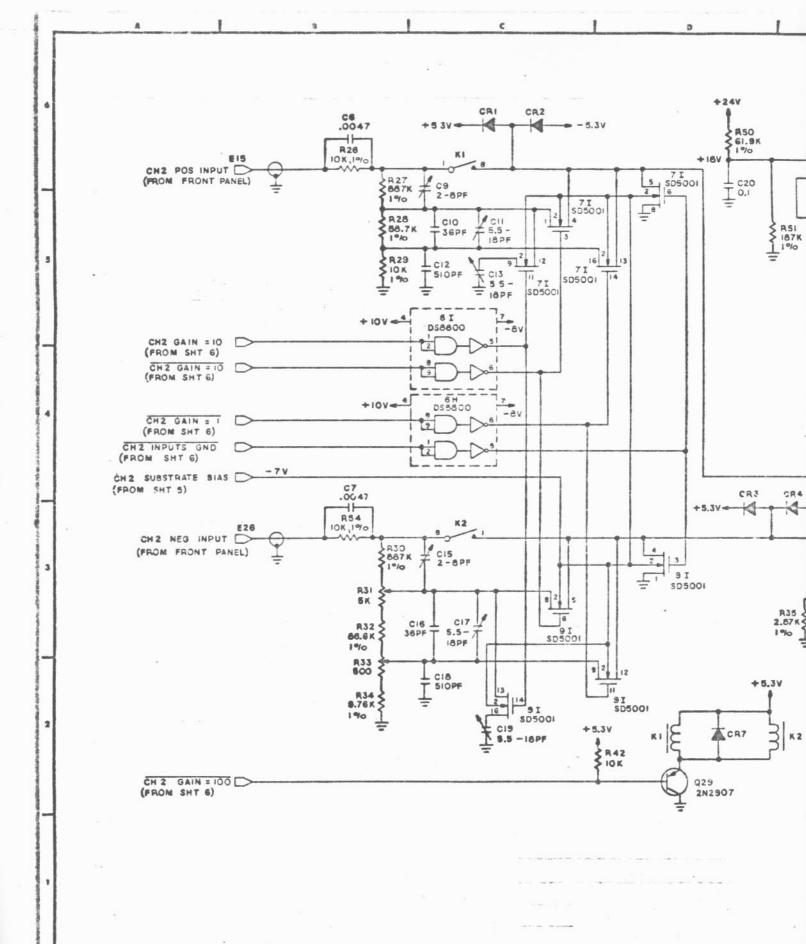

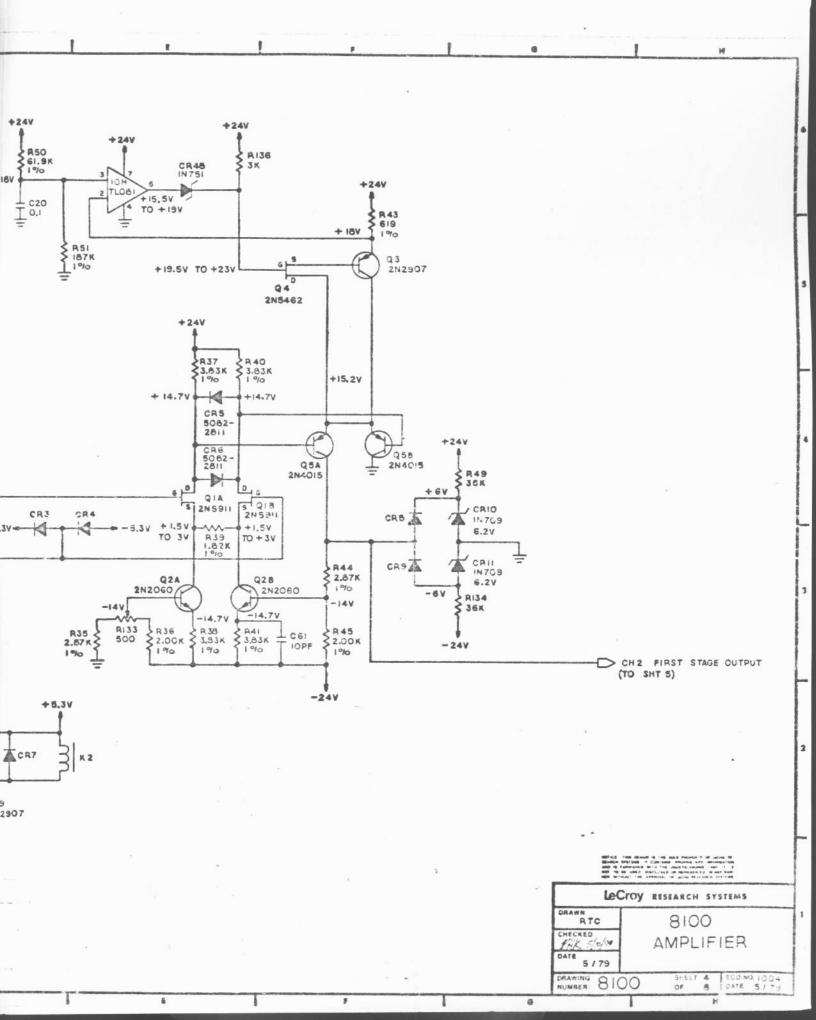

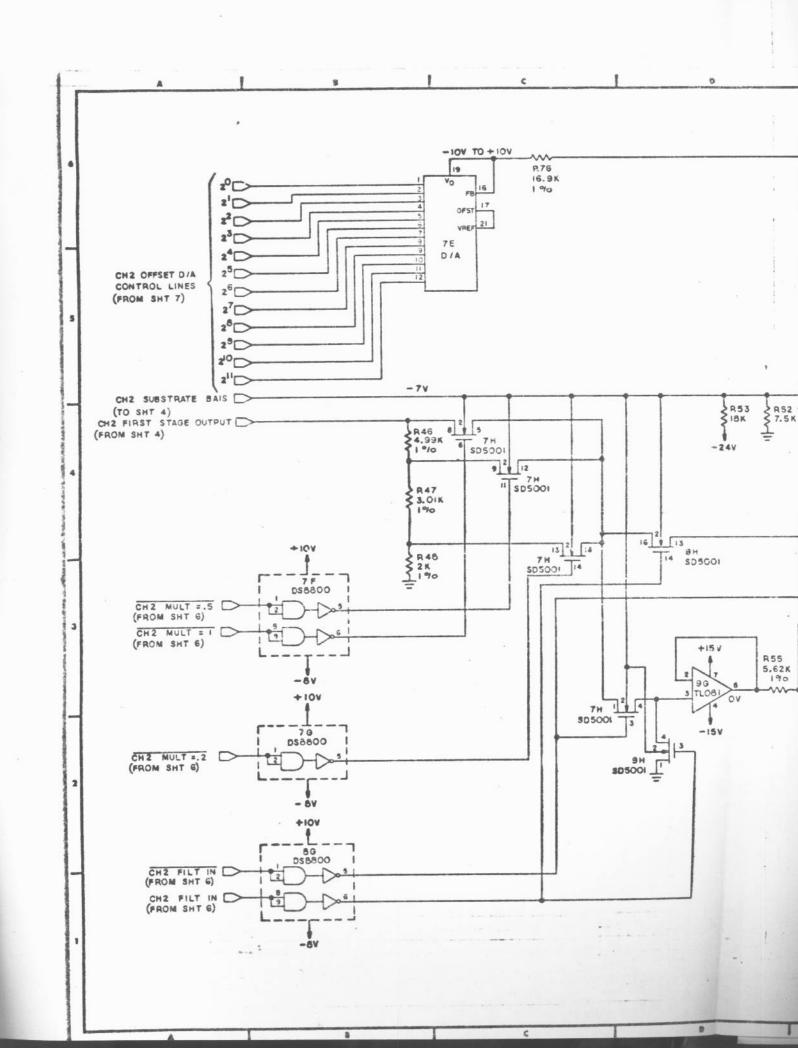

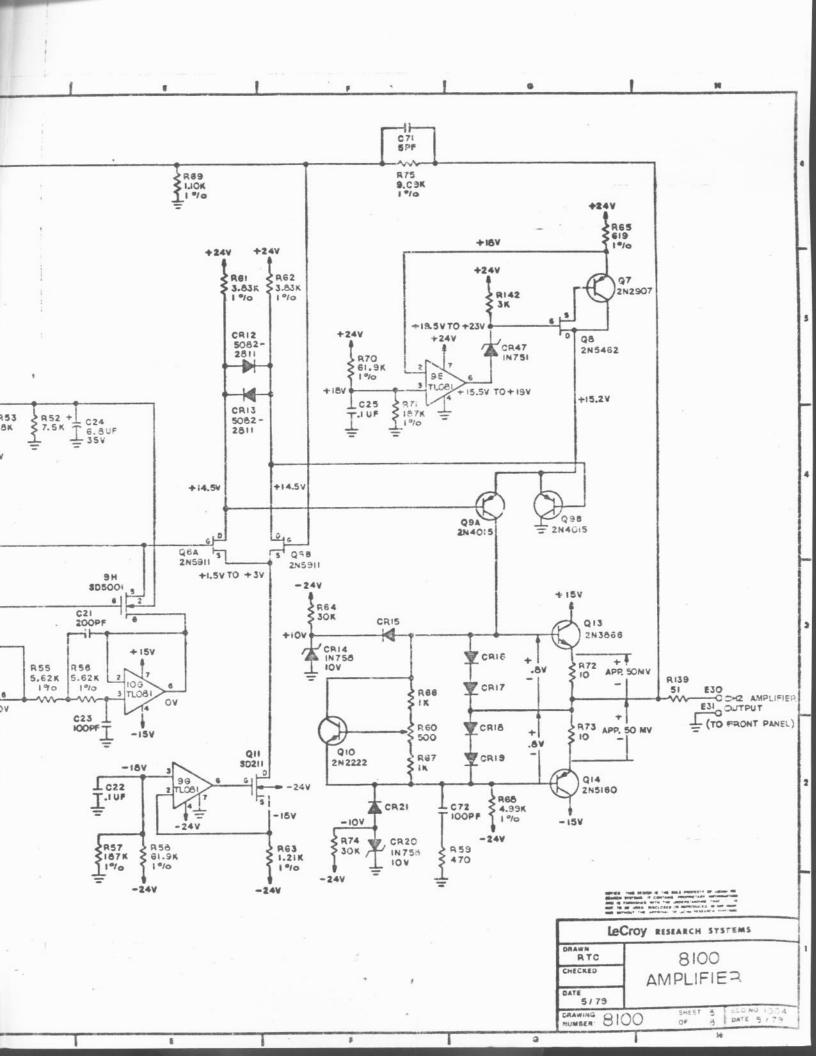

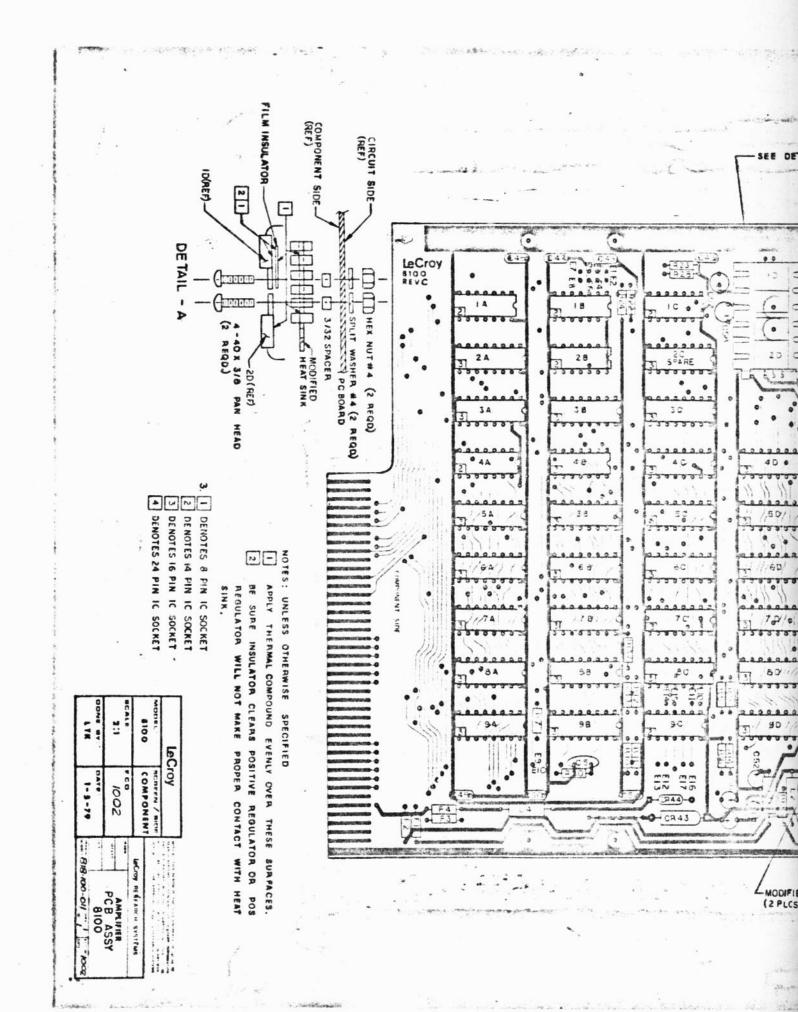

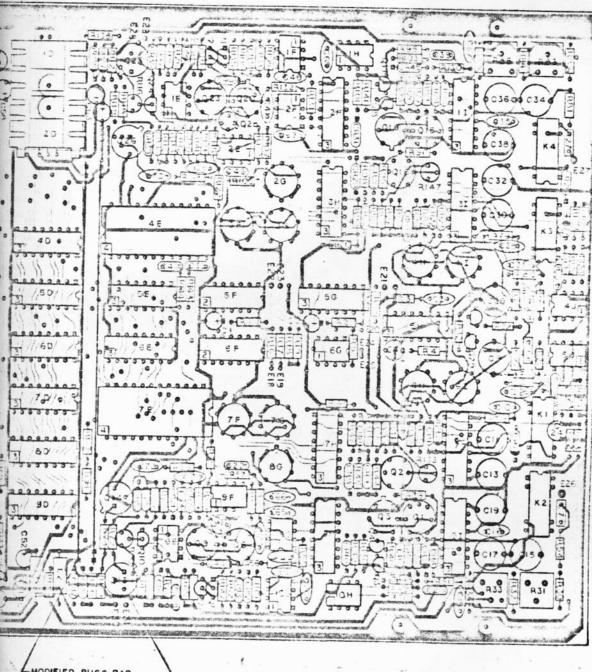

GENERAL: The amplifier used in the 8100 is made up of two separate stages in cascade, each with a gain of 10 and each preceded by a switched attenuator. The input attenuator provides division ratios of 1, 10, and 100, and is controlled by the Gain switch. It is followed by the first gain stage, which accepts differential inputs and provides a single-ended output to the second attenuator. This attenuator provides division ratios of 1, 0.5, and 0.2, and is controlled by the Multiplier switch. The output of the second attenuator drives either the second gain stage input, or the input of the 200 khz filter, if the filter is switched in. The filter is a unity-gain active type, and its output drives the input of the second gain stage if the filter is switched in. The second gain stage includes a power output stage to allow driving 50-ohm loads. This stage is also the point where the offset is injected. The offset voltage is generated by a 12-bit monolitic D/A converter using offset binary code. The 8100 contains two identical channels of the amplifier described above, plus control and CAMAC interface logic.

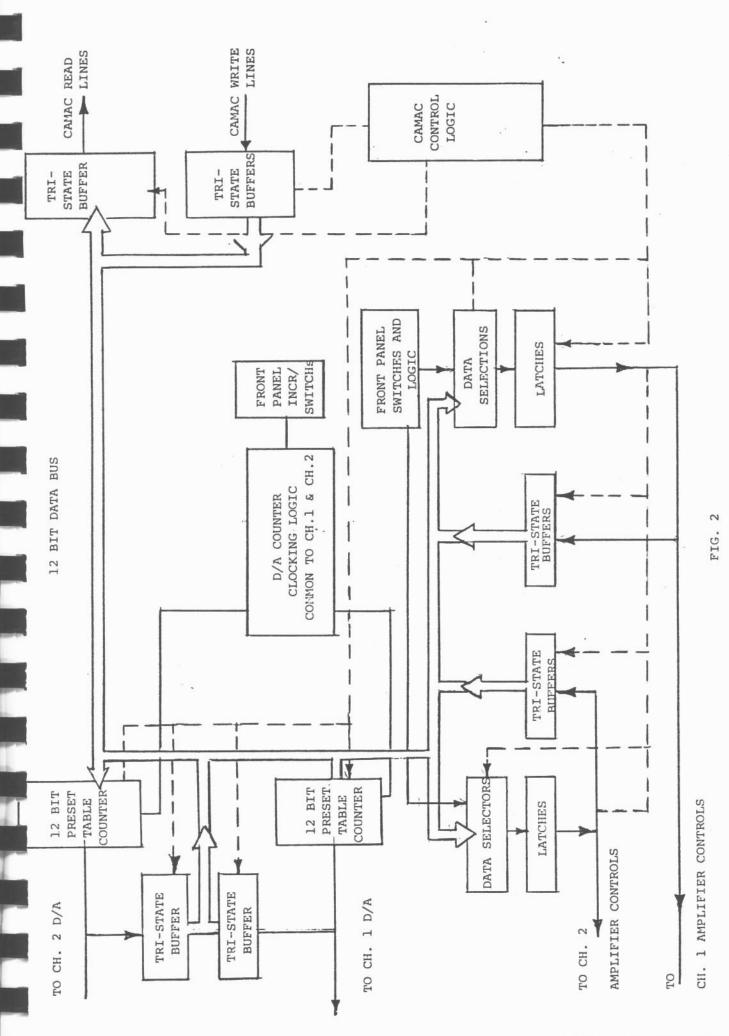

In the following description only the #1 amplifier will be described, plus any circuitry that is common to both. The channel #2 amplifier is identical to the channel #1 amplifier. In the above and following discussions, refer as necessary to the Amplifier Block Diagram, Fig. 1, the Amplifier Logic Block Diagram, Fig. 2, and the schematic

diagrams in the back of this manual.

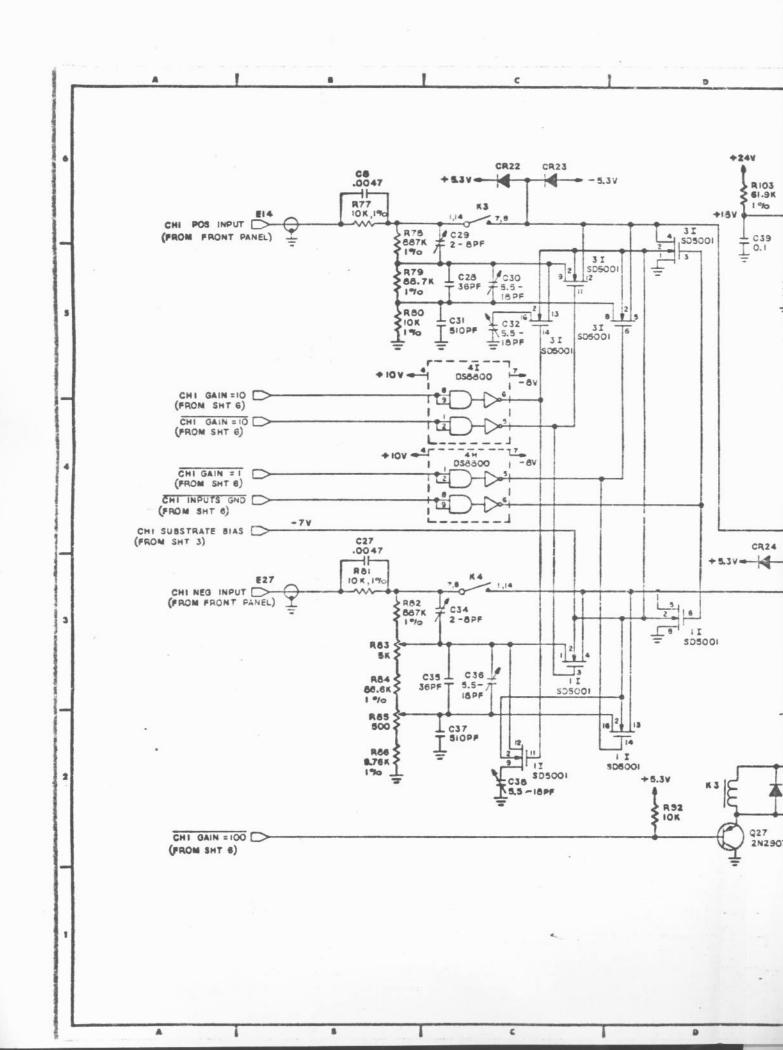

INPUT ATTENUATORS: The input attenuators for the 8100 are capacitor-compensated to allow good square wave response while maintaining 1 megohm impedance. The non-inverting input attenuator is composed of resistors R77-R80 and capacitors C8, and C28-C32. R77, CR22, and CR23 form a voltage limiting network to protect the amplifier input against overvoltage. C32 compensates for the loss of the amplifier's input capacitance when the attenuator is switched into the +100 position. A relay is used in the +1 position to achieve greater common mode voltage range for the +10 and +100 postions.

The inverting input attenuator is essentially the same as the non-inverting attenuator, with the exception of R83 and R85, which are added to allow adjustment of DC common-mode rejection ratio in the +10 and +100 positions.

ICs 4I and 4H translate the TTL drive signals into appropriate voltages to drive the FET switches. Q27 provides power gain to drive the relay coils for K3 and K4.

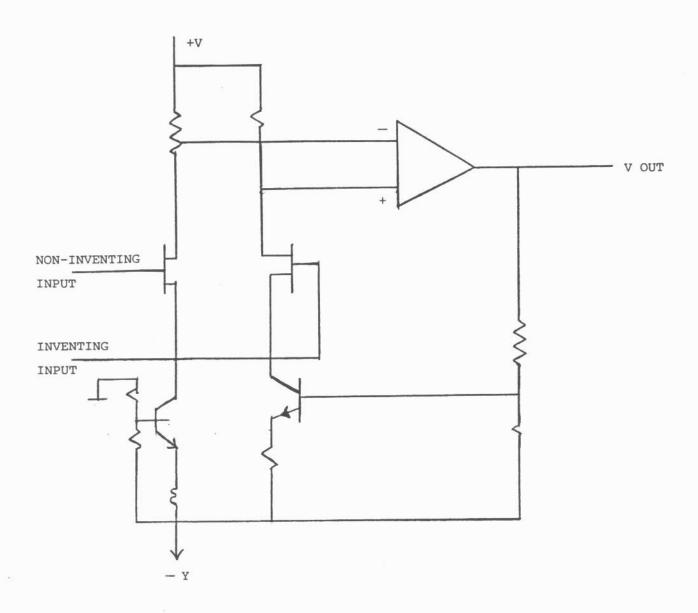

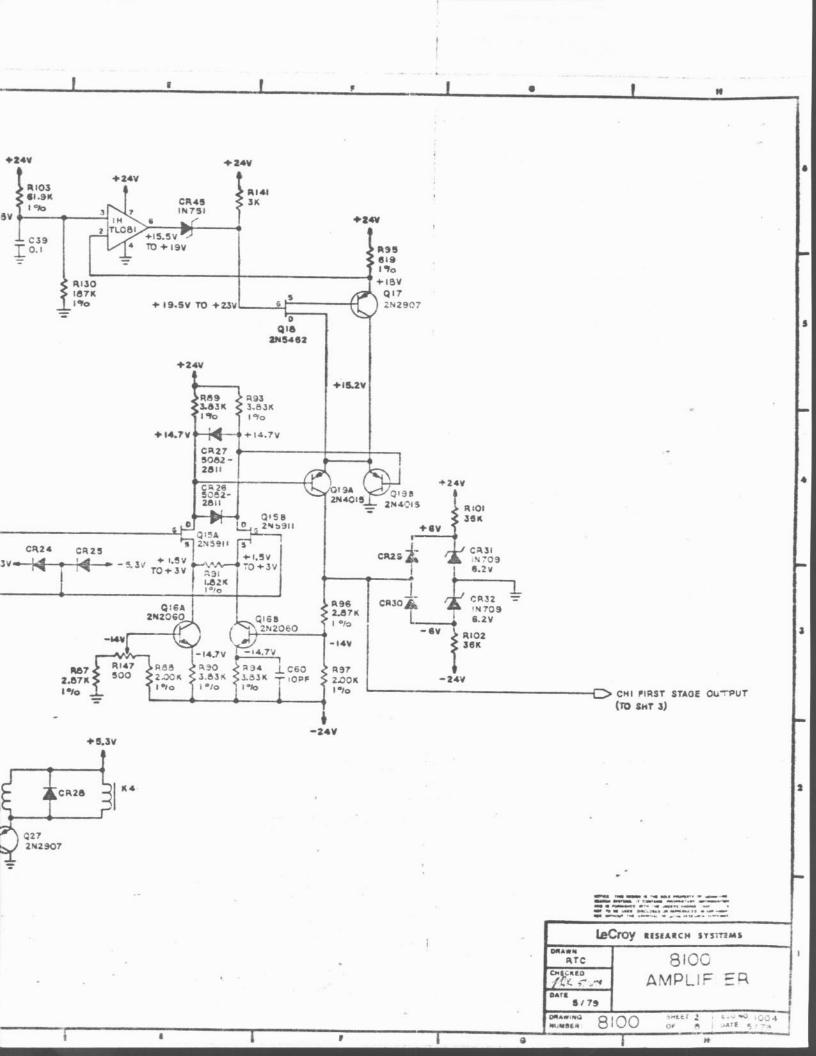

and is used both as an impedance converter and as a differential-to-single-ended converter. A block diagram of the type of circuit used is shown in Fig. 3. Q15 is a matched pair of junction FETs and is used as a defferential input stage, to present a very high inpedance load to the preceding 1 megohm input attenuator. Q19 is another matched pair of transistors which functions as a low drift differential -to-

single-ended converter and principal gain stage. Q17 and Q18, together with amplifier 1H, form a very low drift, high output impedance current source for the emitters of Q19. CR45 prevents output saturation in amplifier 1H. Q16 is another matched pair that acts as a current source bias for Q15 and provides a feedback path for the overall amplifier via divider R96 & R97. Gain of the stage is determined by a combination of R96, R97, R94, and R91, but can be altered easily by changing R91 alone. CR26 & CR27, in addition to CR29-32, limit voltage swings to allow quick recovery from overdrives.

INTERSTAGE ATTENUATOR: The interstage attenuator is an uncompensated resistive attenuator formed by R98-100. Switching is accomplished by 3 of the 4 MOSFETs in 3H.

200KHZ FILTER: The 200 KHZ Filter is an active 2-pole lowpass filter of the Sallen and Key single-amplifier type, with poles placed to acheive a Butterworth (maximally flat gain) response. Amplifier 1F is the active element, with R131, R132, C40, and C41 determining the rolloff point. Amplifier 2F serves as a unity-gain buffer to isolate the filter from the interstage attenuator. Filter switching is done with MOSFETs. An additional MOSFET grounds the filter when it is not in use to minimize noise pickup.

SECOND AMPLIFIER STAGE: The second amplifier stage also has a gain of 10. Q20 is a matched pair of junction FETs and is used as an input stage here to provide a high inpedance load for the interstage attentuator output. It is biased by a current source formed by Q28 and

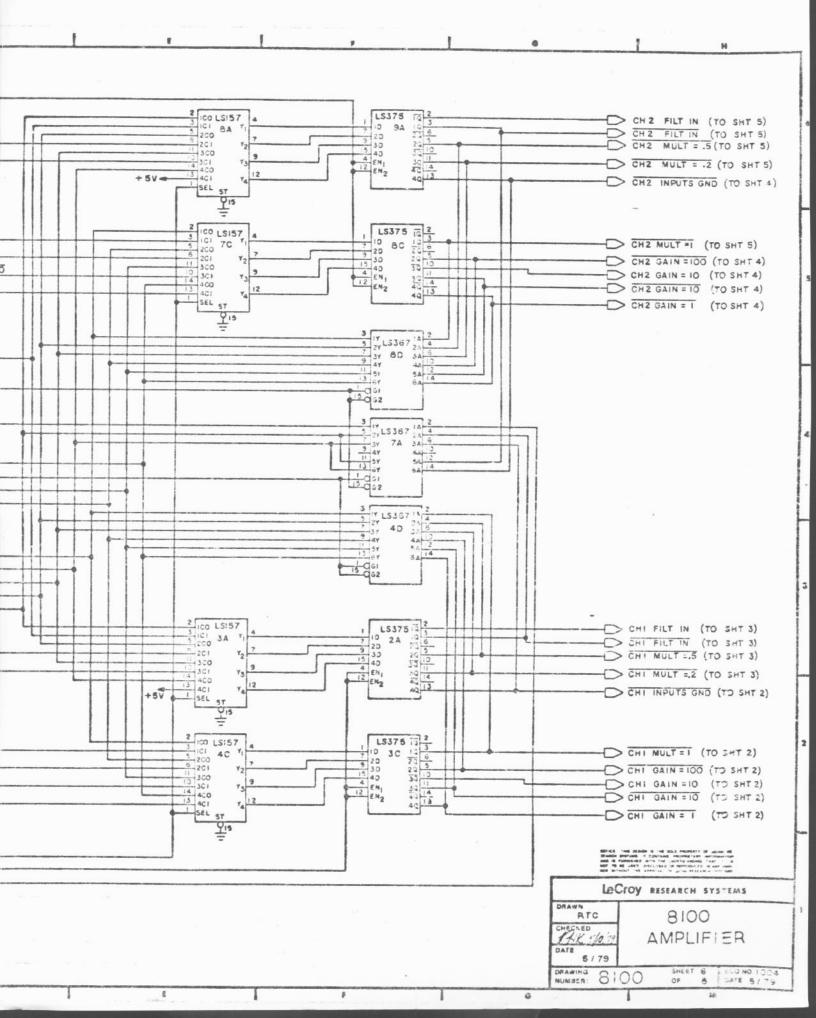

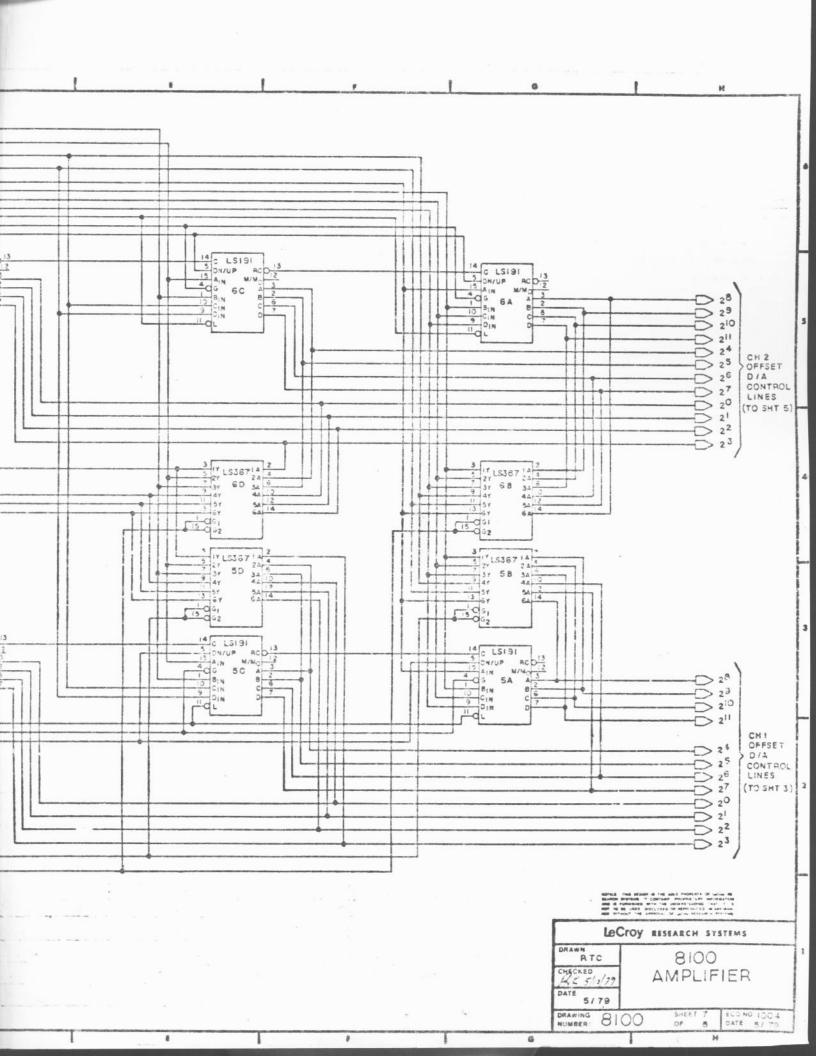

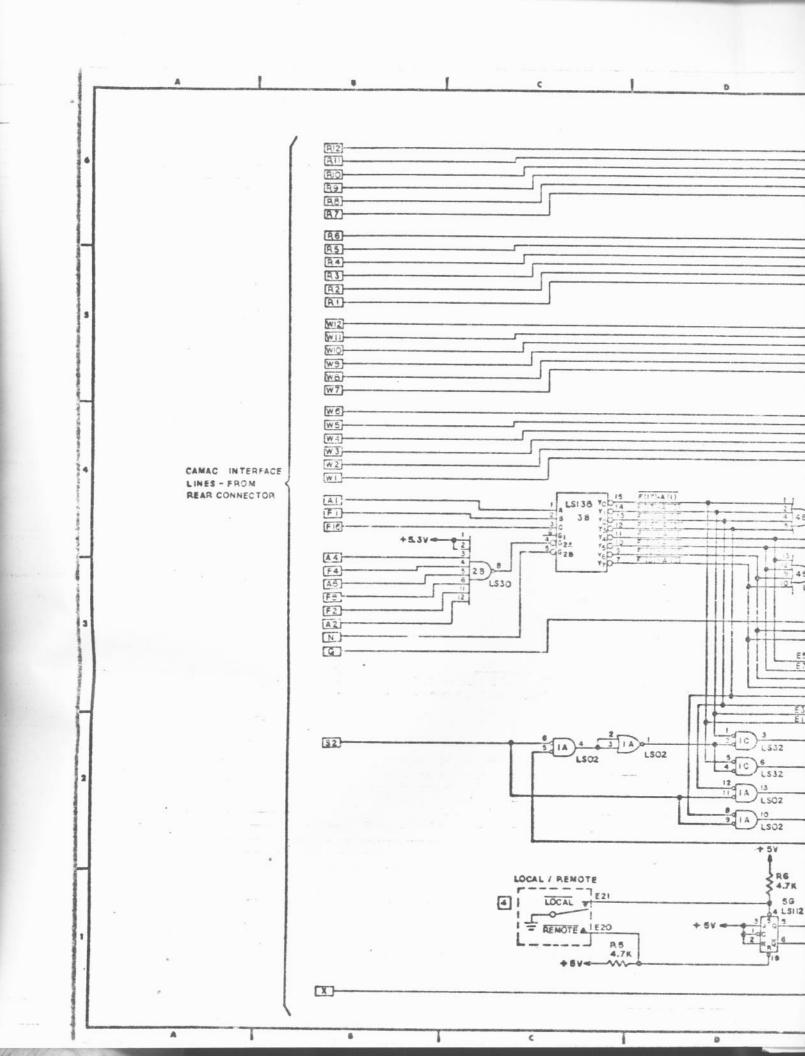

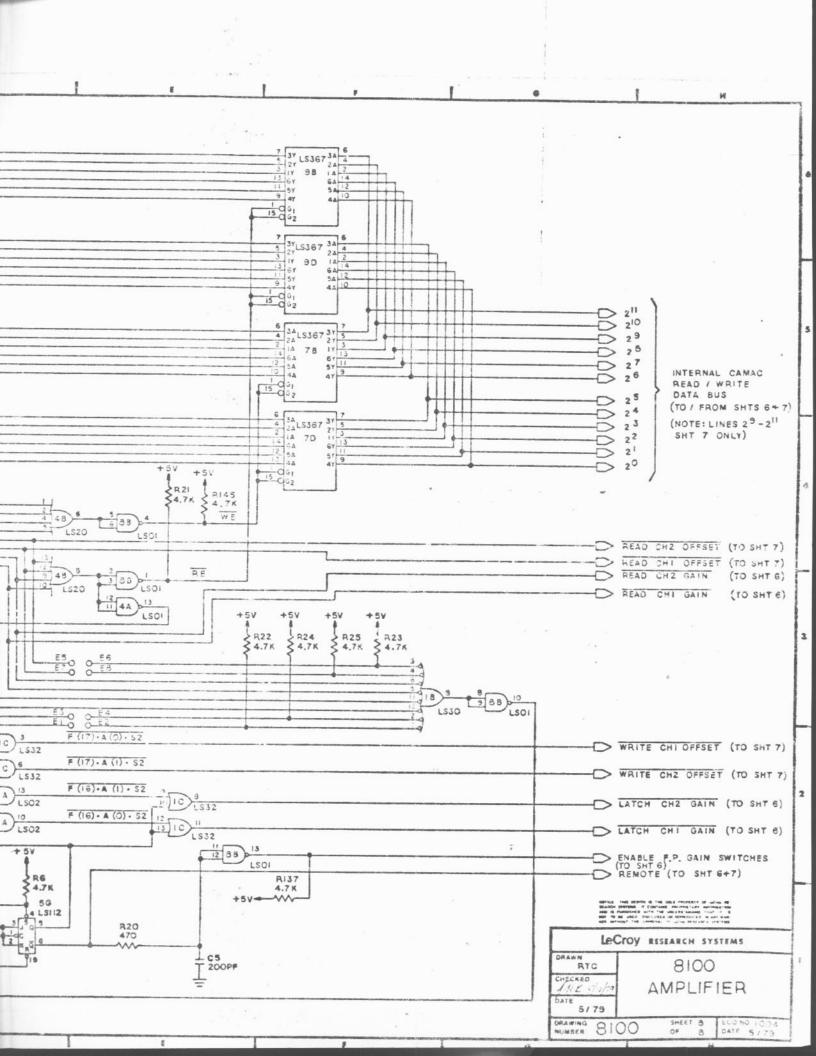

amplifier 2E. 023 is the primary voltage gain stage, and is biased by a current source formed by Q21, Q22, and amplifier 1E, with CR46 preventing output saturation of 1E. Q23 drives a power stage whose primary elements are Q25 and Q26. Rll2 allows adjustment of bias current in Q25 and Q26 by altering the voltage drop across Q24, which also helps temperature compensate that bias current. R115, R121, and R122 determine the closed-loop gain of the stage, with R122 also providing the summing point for the voltage generated by the offset D/A converter (4E). CR33-36, CR41, and CR42 limit voltage swings to improve overdrive recovery. CR37-40, R118, and R119 form a network that limits current in the power stage to protect against short circuits and overloads on the output. R138 sets the output impedance of the amplifier. DIGITAL CONTROL AND CAMAC INTERFACE: CAMAC read and write lines are buffered near the back connector by tri-state buffers 4B, 4D, 7B, and 7D and are combined on a single 12-line read-write bus that services all the digital control circuitry for the unit. This was done partly to reduce trace crowding on the board, but the primary purpose is to keep CAMAC signals near the back of the board when the unit is not addressed in order to reduce interference in the amplifier circuits themselves. Control of the offset D/A converters is provided via two 12-bit, resettable up-down binary counters, formed by 5A, 5C, and 5E for amplifier #1, and 6A, 6C, and 6E for amplifier #2. Count switch decoding is provided by 6F-3, 6F-8 and 5F-8. One-shot 5H-2 debounces the count switches, 5H-10 outputs the single clock pulses and triggers timer 6G,

which provides the 1-second delay before the continuous clock (R1, C1, and 5F-11) is enabled. It should be noted that the clocking circuitry is common to both counters; thus only one count switch should be operated at one time, or extra counts may result.

The counters also serve as latches to hold data from the CAMAC W lines when the offset is controlled via the interface. Data from the internal bus is connected to the counters' preset data lines, and is strobed into the counters in response to commands on the Load inputs via 1C-3 (amplifier #1) and 1C-6 (amplifier #2). Data in the counters is read back onto the internal bus by tri-state buffers 5B and 5D (amplifier #1) and 6B and 6D (amplifier #2).

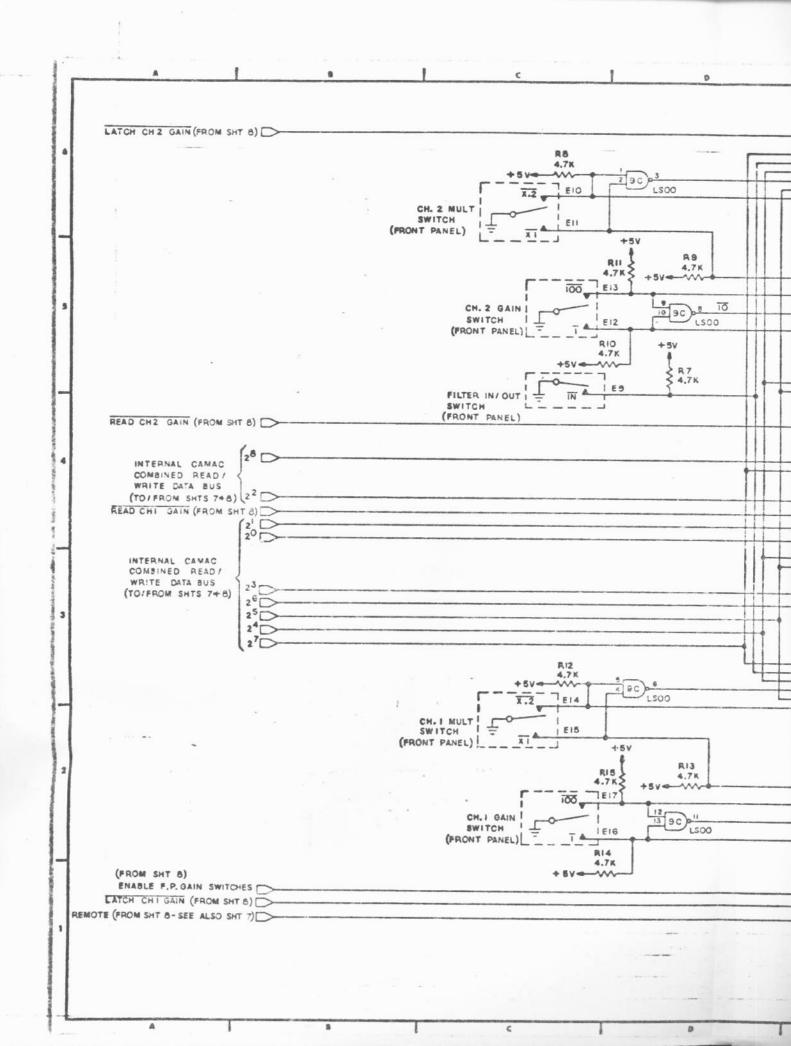

The state of the amplifiers' gain, filters, and grounding is determined by the data stored in latches 2A and 3C (amplifier #1) and 8C and 9A (amplifier #2), which retain data that is output by data selectors 3A-4C and 8A-7C respectively. The selectors choose either the outputs of the switches or the internal data bus as inputs, depending on the state of the Remote/Local switch, which is debounced by flip-flop 5B-5. In Local mode, the latches follow their inputs because 1C-8 and 1C-11 are held high; in Remote mode, however, S2 and the appropriate address and function codes must appear via 1A-10 or 1A-13.

Data in these latches is read back onto the internal data bus via tri-state buffers 4D, 7A, and 8D.

CAMAC commands are decoded by 2B and 3B. Write lines or Read lines are enabled by 4B-6 through 8B-4 or 4B-8 through 8B-1, respectively.

8100 AMPLIFIER LOGIC BLOCK DIAGRAM

FIG. 3

FIRST AMPLIFIER STAGE BLOCK DIAGRAM

| DATE     | PRIORITY | NOTERTROPER                                                                      |

|----------|----------|----------------------------------------------------------------------------------|

|          | -        | NECKLETION                                                                       |

|          |          | NOT USED                                                                         |

| 6/28/19  |          | CORRECT LAYOUT ERRORS ON "B" REV. AND PARTS LIST CHANGES                         |

| . 61/4/6 |          | REF. DESIGNATION CHANGES AND PARTS LIST                                          |

| 9/18/79  |          | PCB SILKSCREEN AND ARTWORK CHGS., ASSY DWG, PARTS LIST AND SCHEMATIC CHANGES     |

| 9/27/79  |          | RESISTOR CHANGE, ASSY DWG CHANGE TO IMPROVE AMPLIFIER GAIN AND PARTS LIST CHANGE |

|          |          |                                                                                  |

|          |          |                                                                                  |

|          |          |                                                                                  |

|          |          |                                                                                  |

|          |          |                                                                                  |

|          |          |                                                                                  |

|          |          |                                                                                  |

|          |          |                                                                                  |

|          |          |                                                                                  |

|          |          |                                                                                  |

| 62       |          |                                                                                  |

|          |          |                                                                                  |

|          |          |                                                                                  |

|          |          |                                                                                  |

|          |          |                                                                                  |

| 2        | 2        |                                                                                  |

|          |          |                                                                                  |

|          |          |                                                                                  |

Remarks: On Priorities 1-Recall, field retrofit 2-Rework shippable units 3-Rework units in fabrication, assembly or test 4-Improvements for future MO's

OCITAIE LEESS SOLLVIO NA

| CHECKED | ENGINEERING CHANGE ONDERS |

|---------|---------------------------|

| DATE    | MODEL: 8100               |

BASIC

CAMAC DATAWAY

OPERATING INFORMATION

Condensed from:

Document EUR 4100e

Published by the:

Esone Committee of the Joint Nuclear Research Center Ispra Establishment -- Italy March 1969

#### INTRODUCTION

CAMAC is an international standard of modularized electronics as defined by the ESONE Committee of the JNRC, Ispra. Its function is to provide a scheme to allow a wide range of modular instruments to be interfaced to a standardized multi-receptacle which, in turn, may be interfaced to a computer. In this way, additions to a data transfer and control system may be made by plugging-in additional modules and making suitable software changes. Thus, CAMAC allows information to be transfered into and out of the instrument modules.

CAMAC modules may be plugged into a <u>CAMAC Crate</u> which has 25 <u>Stations</u>, numbered I through 25. Station 25, the rightmost station, is reserved for a <u>Crate Controller</u>, whereas Stations I - 24 are <u>Normal Stations</u> used for <u>CAMAC Modules</u>. Usually, Station 24 is also used by the <u>controller</u> in that most controllers are double width (#2 CAMAC). The purpose of the <u>controller</u> is to issue <u>CAMAC Commands</u> to the modules and transfer information between a computer (or other digital device) and the <u>CAMAC modules</u>.

Data transfer, control functions, and module powering is affected via the <u>Dataway</u>. This is a series of bus and individual lines across the back of the crate. The dataway lines include digital data transfer lines, strobe signal lines, and addressing lines and control lines. See Page 18C for a pin allocation chart.

In a typical dataway operation, the crate controller issues a <u>CAMAC Command</u> which includes specifying a station number (N), a subaddress (A), and function code (F) (see Page 17C). In response, the subaddress of the module will generate valid command accepted (X response) and act on the command. If this command requires data transfer, the read (R) or write (W) lines will be used. Note that the terms Read and Write apply to the controller, not the module. For example, under a read command, the controller reads data contained within a module.

#### USE OF THE DATAWAY LINES

Communication with plug-in units takes place through the Dataway. This passive multi-wire highway is incorporated in the crate and links the 86-pin sockets to all stations. The bus-lines link corresponding pins at all normal stations and, in some cases, the control station. Individual lines link one pin at a normal station to one pin at the control station. The patch pins have no specified Dataway wiring but can be connected to individual points to which patch leads may be attached.

During a Dataway operation the controller generates a command consisting of signals on individual Station Number lines to specify one or more modules, signals on the Subaddress bus-lines to specify a sub-section of the module or modules, and signals on the Function bus-lines to specify the operation to be performed. The command signals are accompanied by a signal on the Busy bus-line, which is available at all stations to indicate that a Dataway operation is in progress.

When a module recognizes a Read command, calling for a data transfer to the controller, it establishes data signals on the Read bus-lines. When a controller recognizes a Write command calling for a data transfer to a module, it establishes data signals on the Write bus lines. In addition, regardless of whether there is transfer on the R or W lines, the module may transmit one bit of status information on the Response bus-line.

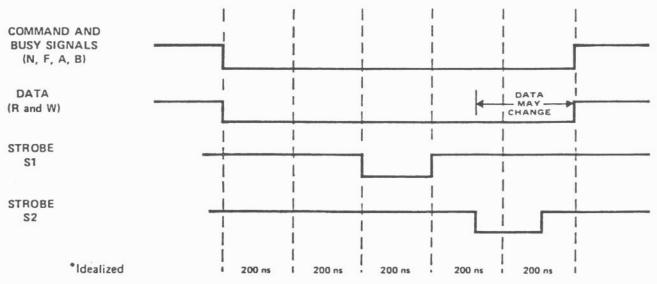

Two timing signals, Strobes SI and S2, are then generated in sequence on separate bus-lines. The strobes are used to transfer data from the Dataway into modules (on Write commands) and into the controller (on Read commands). They may also initiate other actions within the controller and modules.

Whenever there is no Dataway operation in progress (indicated by the absence of the Busy signal) any module may generate a signal on its individual Look-at-Me line to indicate that is requires attention. Three common controll signals are available at all stations, without requiring addressing by a command, in order to Initialize all units (typically after switch-on), to Clear data registers, and to Inhibit features such as data-taking.

#### **DEFINITION OF COMMANDS**

A command consists of signals on the Dataway lines which specify at least one module (by individual station number lines), a sub-section of the module or modules (by the four sub-address bus-lines), and the function to be performed (by the five function bus-lines). The command signals are maintained for the full duration of the operation on the Dataway. They are accompanied by a signal on the Busy bus-line which indicates to all units that a Dataway operation is in progress.

#### Station Number (N)

Each normal station is addressed by a signal on an individual station number line (N) which comes from a separate pin at the control station. The stations are numbered in decimal code from the left-hand end as viewed from the front, beginning with Station 1.

#### Sub-Address (A8, A4, A2, A1)

Different sections of a module are addressed by signals on the four A bus-lines. These signals are decoded in the module to select one of up to sixteen sub-addresses, numbered in decimal from 0 to 15.

# Function (F16, F8, F4, F2, F1)

The function to be performed at the specified sub-address in the selected module or modules is defined by the signals on the five F bus-lines. These signals are decoded in the module to select one of up to 32 functions, numbered in decimal from 0 to 31. The definitions of the 32 function codes are summarized in the Dataway Command Operations section.

# Strobe Signals (S1 and S2)

Two strobe signals S1 and S2 are generated in sequence on separate bus-lines. These signals are used to transfer information between plug-in units via the Dataway or to initiate operations within units. In either case the specific action is determined by the command present on the Dataway. Both strobes are generated during each Dataway command operation, and all plug-in units which accept information from the Dataway do so in response to these strobes. The first strobe S1 is used for actions which do not change the state of signals on the Dataway lines. All units which accept data from the Dataway in a Read operation, or in a Write operation do so in response to S1. The second strobe S2 is used to initiate any actions which may change the state of Dataway signals, for example, clearing a register whose output is connected to the Dataway.

#### DATA

A common parallel highway is used for all transfers. All information carried by the parallel highway is conveniently described as data, although it may be information concerned with status or control features in modules. Up to 24 bits may be transferred in parallel between the controller and the selected module. Independent lines (Read and Write) are provided for the two directions of transfer.

#### The Write Lines (W1-W24)

The controller or other common data source generates data signals on the W bus-lines at the beginning of any 'Write' operation. The W signals reach a steady state before S1, and are maintained until the end of the operation, unless modified by S2.

#### The Read Lines (R1-R24)

Data signals are set up on the R bus-lines by the module as soon as a "Read" command is recognized. The R signals reach a steady state before S1, and are maintained for the full duration of the Dataway operation, unless the state of the data source is changed by S2. The controller or other common data receiver strobes the data from the R bus-lines at the time of the Strobe S1.

#### STATUS INFORMATION

Status information is conveyed by signals on the Look-at-Me (L), Busy (B), and Response (Q) lines.

#### Look-at-Me (L)

This, like the N line, is an individual connection from each station to a separate pin at the control station. When there is no Dataway operation in progress (no B present) any plug-in unit may generate a signal on its L line to indicate that it requires attention. When B is present each L signal is gated off the Dataway line by the unit which generates it.

A Look-at-Me request can be reset by Clear Look-at-Me, Initialize, or by the performance of the specific action which generated the request.

#### Dataway Busy (B)

The Busy signal is used to interlock various aspects of a system which can compete for the use of the Dataway. Specifically, it is generated during Dataway command or common control operations. Whenever N is present, B is present, and for the duration of B, all L signals are gated off the Dataway lines.

#### Response (Q)

The Q bus-line is used during a Dataway operation to transmit a signal indicating the status of a selected feature of the module.

On all Read and Write commands the signal on the Q bus-line remains static from the time the command is received until S2. For all other commands the signal on the Q bus-line may change at any time.

#### COMMON CONTROLS

Common control signals operate on all modules connected to them, without requiring to be addressed by a command. In order to provide protection against spurious signals the Initialize (Z) and Clear (C) signals must be accompanied by Strobe S2.

#### Initialize (Z)

The Initialize signal has obsolute priority over all other signals or controls. It sets all units to a basic state by resetting all resetting all registers, whether data or control, to a defined state, and by resetting all L signals and disabling them where possible. Units which generate must also cause S2 and B to be generated. Modules which accept Z gate it with S2 as a protection against spurious signals on the Z line.

#### Inhibit (I)

The presence of this signal inhibits any activity (for example, data taking). It must either not change when B is present or have rise and fall times not less than 200 ns.

# Clear (C)

This common signal clears all registers or bistables connected to it. Units which generate C must also cause S2 and 3 to be generated. Modules which accept C gate it with S2 as a protection against spurious signals on the C line.

#### PRIVATE WIRING

# Patch Leads (P1-P7)

Five pins (P1 to P5) on the 86-way socket at normal stations are not prewired to Dataway lines but are freely available for local connections. At the control station seven pins (P1-P7) are available. Signals on the patch pins must either remain static when B is present or have rise and fall times not less than 20 ns.

#### DATAWAY COMMAND OPERATIONS

A command is composed of signals on the Station Number line or lines, the Sub-Address lines and the Function lines. It is accompanied by a signal on the Busy Line. In response to a command, data may be transferred on the Read or Write lines and one bit of status information on the Q line. The two Strobes S1 and S2 must be generated in each Dataway command operation and control its timing.

The order in which the commands are described below corresponds to the function codes set out in Table 2. In this table the term 'register' is used for an addressable data source or receiver, without implying that it has a data storage property. The function codes allow the registers in a module to be divided into two distinct sets, known as Group 1 and Group 2. Thus it is possible to operate on more than the basic set of 16 registers selected by the 4 sub-address lines.

A common feature of all commands is that if the module has a Look-at-Me source which requests a specific command then the performance of that command should be reset the Look-at-Me source.

# Read Commands (Function Codes 0-7)

Read commands are identified by the combination F16 = 0, F8 = 0 in the function code. They specify that information is to be transferred from a module to a controller via the R bus-lines. Data signals are set up on the R bus-lines by the module as soon as the 'Read' command is recognized, and the appropriate status signal connected to the Q bus-line. The R and Q signals reach a steady state before S1, and are maintained for the full duration of the Dataway command operation unless the state of the signal source is changed at S2. The controller or other common data receiver strobes the data from the R and Q bus lines at the time of the strobe S1.

In order to facilitate reading by sequential addressing, all registers containing data (as opposed to control information) must have cosecutive sub-addresses starting at sub-address 0. At each of these sub-addresses the module generates Q=1 in response to the appropriate Read command. At the next sub-address in sequence (where there is not a data register) the response is Q=0. At all remaining sub-addresses the Q signal may be used to test any feature, subject to the general requirement that the Q signal must be static from the beginning of command until at least S2.

#### Code 0, Read Group 1 Register

This command selects, by sub-address, one register from the first group in the module and transfers the contents of this register to the controller. The contents of the register remain unchanged.

#### Code 1, Read Group 2 Register

Same as Code 0, except command selects register from the second group.

#### Code 2, Read and Clear Group 1 Register

Same as Code 0, except the module register is cleared at time S2.

# Code 3, Read Complement of Group 1 Register

Same as Code 0, except command transfers the complement of the contents of this register to the controller.

# Code 4 - 7

Unassigned at this time.

# CONTROL COMMANDS (Function Codes 8 - 15)

Control commands are identified generally by F8 = 1 in the function code. They are divided into two groups by the state of F16, in this case F16 = 0. They specify that information is not transferred on either the R or W bus-lines. However, information may be conveyed on the Q bus-line in any of these commands. The signal on the Q bus-line may change at any time but is strobed into the controller at time S1 and may (except in Code 8) be reset by strobe 2.

#### Code 8, Test Look-at-Me

This command selects a Look-at-Me source in the module and presents the state of this source on the Q bus-line.

#### Code 9, Clear Group 1 Register

This command selects, by sub-address, a register from the first group in the module and clears the contents of this register.

#### Code 10, Clear Look-at-Me

Same as Code 8, except the Look-at-Me source is cleared at time S2.

#### Code 11, Clear Group 2 Register

Same as Code 9, except command selects register from the second group.

#### Code 12-15

Unassigned at this time.

# WRITE COMMANDS (Function Codes 16-23)

Write commands are identified by the combination F16 = 1, F8 = 0 in the function code. They specify that information is to be transferred from a controller to a module via the W bus-lines. The controller or other common data source generates data signals on the W bus-lines at the beginning of the "Write" operation. The module connects the appropriate status signal to the Q bus-line as soon as the command is recognized. The W and Q signals reach a steady state before S1 and are maintained for the full duration of the Dataway command operation unless the status of the signal source is changed at Strobe 2. In order to facilitate writing into registers by sequential addressing, all registers which are to contain data (as opposed to control information) have consecutive sub-addresses starting at sub-address 0. At each of these sub-addresses the module generates Q - 1 in response to the appropriate Write function. At the next sub-address in sequence (where there is not a data register) the response is Q = 0. At all remaining sub-addresses the Q signal may be used to test any feature subject to the general requirement that the Q signal must be static from the beginning of the command until at least S2.

#### Code 16, Overwrite Group 1 Register

This command selects, by sub-address, one register in the first group in the module and sets the contents of this register to correspond with the data generated on the W bus-lines by the controller.

#### Code 17, Overwrite Group 2 Register

Same as Code 16, except command selects register in the second group.

# Code 18, Selective Overwrite Group 1 Register

Same as Code 16, except a separate "mask" register defines which bits in the selected register are set.

#### Code 19, Selective Overwrite Group 2 Register

Same as Code 18, except command selects register in the second group.

#### Code 20 - 23

Unassigned at this time.

# CONTROL COMMANDS (Function Codes 24 - 31)

Control commands are identified generally by F8 = 1 in the function code. They are divided into two groups by the state of F16, in this case F16 = 1. They specify that information is not transferred on either the R or W bus-lines. However, information may be conveyed by the Q bus-line in any of these commands. The signal on the Q bus-line is permitted to change at any time but is strobed into the controller at time S1 and may (except in Code 27) be reset by strobe S2. Precautions must be taken to ensure that information is not lost due to Q signals appearing between S1 and S2.

# Code 24, Disable

This command selects, by sub-address, and disables a feature of the module; e.g., a Look-at-Me source or a data input.

# Code 25, Increment Preselected Registers

This command adds one simultaneously to the contents of each register in one of 16 groups, defined by the sub-address.

#### Code 26, Enable

This command enables the feature of the module selected by the sub-address, e.g., a Look-at-Me source or a data input.

#### Code 27, Test Status

This command selects, by sub-address, any feature of a module other than a source of a Look-at-Me request, and tests it by producing a response on the Q bus-line.

#### Code 28 - 31

Unassigned at this time.

#### DIGITAL SIGNAL STANDARDS ON THE DATAWAY

The potentials for the binary digital signals on the Dataway lines have been defined to correspond with those for compatible current sinking logic devices (e.g., the TTL and DTL series). The signal convention has, however, been inverted to be negative logic. The high state (more positive potential) corresponds to logic '0' and the low state (near ground potential) corresponds to logic '1'. Intrinsic OR outputs are thus available from the manufacturers' standard product range, and disconnected inputs go to the '0' state.

It is an essential feature of the Dataway that many units may have their signal outputs connected to the Read and Response lines. Outputs onto these lines therefore require intrinsic OR gates. The same principle is extended to other lines (Command, Write, etc.) in order to allow more than one controller-like unit in a crate. The Inhibit line may be an exception, since its signals are shaped with a slow rise and fall if they change during Dataway operations.

#### Voltage standards for Dataway Signals

All Dataway Signals must conform to the voltage levels as follows:

Pull-up current sources for all Dataway bus-lines are located in the crate controller (occupying the control station and at least one other station) so as to insure that there is one and only one current source per line. The minimum pull-up current when the Dataway line is at +3.5 V is defined in Table 4 as 2.5 mA but, if the controller generates Dataway signals at time intervals near the permitted minima, the pull-up current sources should preferably provide not less than 6 mA when the lines are at this potential. The pull-up for the N signals is located in the unit generating the signals and for the L signals in the unit receiving the signals so that the individual lines may be joined or grouped within these units if desired.

The N and L lines are effectively individual lines joining two units (a module and a controller) together. The Q and R lines will generally have many units generating the signals (say 20) with a few units (maximum 4) receiving the signals. The remaining lines (W, A, F, S, B, Z, I, C) will have relatively few units generating each signal (often only one) with the possibility of many units receiving the signals.

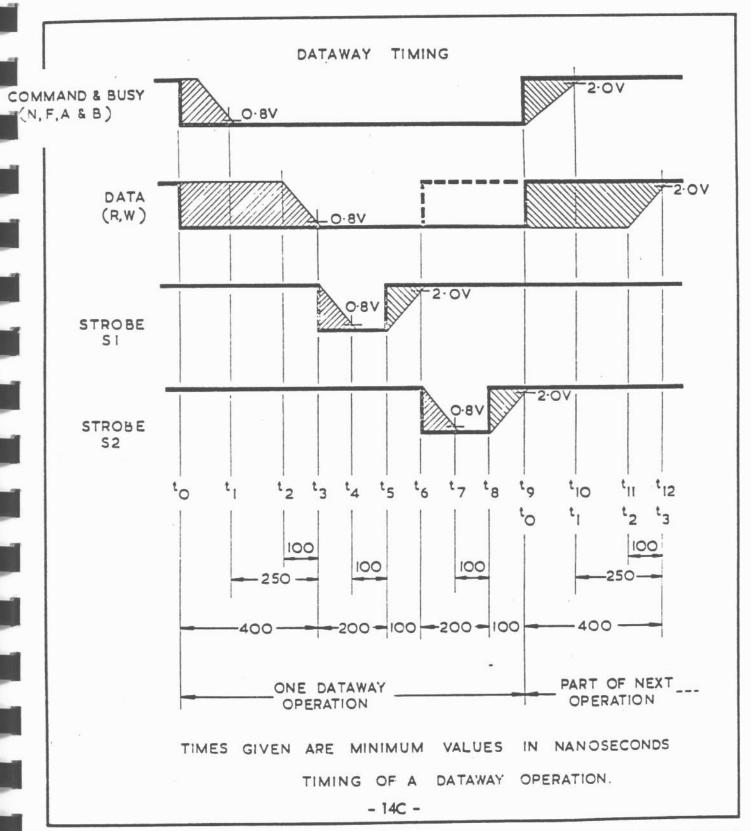

# Timing of Dataway Signals

The sequence of events during a single Dataway operation is shown in Timing Diagram, Page 13C, by means of simplified signal waveforms. The shaded areas indicate the permitted variation of each signal between an ideal square signal and a signal whose transition across the appropriate signal threshold (0.8 V or 2.0 V) satisfies the conditions shown. The signal waveforms for the command and data lines apply to those lines, if any, which take up the '1' state. Other command and data lines may, of course, be in the '0' state during the operation.

The signals on the Busy line and the various signals constituting the command need not occur in exact synchroism, provided their envelope lies within the shaded areas of the diagram. Similar variation is permitted between the signals constituting the data. The broken line indicates the earlies time at which the data signals may change in response to S2.

Key points on these waveforms are indicated by t<sub>0</sub> - t<sub>9</sub>, with the following significance:

Points t<sub>0</sub>, t<sub>3</sub>, t<sub>6</sub> represent the initiation of the negative-going of the Command, Strobe 1, and Strobe 2 signals, respectively. They are the times at which the signals would be received from an ideal Dataway with no capacitative loading.

Points to, to, to represent similarly the initiation of the positive-going edges of the same signals.

Points t<sub>2</sub>, t<sub>11</sub> are the latest times at which the data source is permitted to initiate the negative-going and positive-going edges of the data signals.

Points  $t_1$ ,  $t_3$ ,  $t_4$ ,  $t_7$  represent the latest times at which the received signals are permitted to reach a maintained '1' state, and therefore refer to the last negative-going transition across the + 0.8 V threshold.

Points  $t_6$ ,  $t_9$ ,  $t_{10}$ ,  $t_{12}$  represent the latest times at which the received signals are permitted to reach a maintained '0' state, and therefore refer to the last positive-going transition across the +2.0 V threshold.

Controllers must initiate the negative and positive going edges of the command and strobe signals at intervals not less than those defined by  $t_3$ ,  $t_5$ ,  $t_6$ ,  $t_8$  and  $t_9$ . Modules respond to the command within the most adverse value of  $(t_1 - t_2)$ ; i.g., 100 ns. The electrical characteristics of the Dataway and connections from it into units must allow signals to rise and fall within the minimum times for  $(t_0 - t_1)$ ,  $(t_2 - t_3)$  etc.

The next Dataway operation must not start before to.

The extreme case is shown in Timing Diagram, Page 15C, with the next operation starting at to, so that to - to of one operation coincide with to - to of the next. The command and data signals of one operation may thus be removed while those of the next operation are being established. The Busy signal may be maintained continuously during a sequence of consecutive Dataway operations. Under suitable conditions any command or data signals of one operation may thus be removed while those of the next operation are being established. The Busy signal may be maintained continuously during a sequence of consecutive Dataway operations. Under suitable conditions any command or data signals which have the same state during successive operations may also be maintained. In the extreme case of successive operations with the same command and data there could be a complete absence of signal transitions between to and to.

ENGINEERING DEPARTMENT LeCroy Research Systems Corp.

#### **POWER SUPPLIES**

The voltage tolerances and current loadings are specified below. The specified tolerances in voltage refer to the voltage measured at the contacts of the Dataway sockets and must be maintained under the worst combination of factors such as a.c. mains voltages and frequency, the maximum current loadings, temperature and the position in the crate of the socket under observation.

Note that the maximum currents stated in the below table are subject to the over-all restrictions as follows:

- The current carried by any contact of the Dataway socket must not exceed 3 A.

- 2. The total power dissipated in a crate, without forced ventilation, must not exceed 200 W.

- 3. The power dissipation per single width station should not, therefore, normally exceed 8 W; however, under special circumstances this rating may be increased to a maximum of 25 W provided suitable precautions are taken to comply with total power dissipation and current loadings.

The resistance between any point on the Dataway OV power return bus-line and the point at which the power supply is joined to the crate wiring must not exceed 2 milliohms.

|                                                      |                                   | Maximum Current Loads                                              |                                       |  |  |

|------------------------------------------------------|-----------------------------------|--------------------------------------------------------------------|---------------------------------------|--|--|

| Supply<br>Voltage                                    | Voltage<br>Tolerance              | In the Plug-in<br>(per unit width)<br>See Notes (1) & (3)<br>Above | In the crate<br>See Note (2)<br>Above |  |  |

| Mandatory                                            |                                   |                                                                    |                                       |  |  |

| +24V d.c.<br>+ 6V d.c.<br>- 6V d.c<br>-24V d.c<br>OV | ± 0.5%<br>±2.5%<br>±2.5%<br>±0.5% | 1A<br>2A<br>2A<br>1A                                               | 6A<br>25A<br>25A<br>6A                |  |  |

| Additional (as req                                   | uired)                            |                                                                    |                                       |  |  |

| +200V d.c.<br>+ 12V d.c.<br>- 12V d.c.               | +60V, -20V<br>± 0.5%<br>± 0.5%    |                                                                    | 0.1A                                  |  |  |

| 117V a.c.                                            | +10%, -12%                        |                                                                    | 0.5A                                  |  |  |

### **CAMAC** Reference Data

### **CAMAC FUNCTION CODES**

| CODE                 |                                                                                                                     |                  | FUNC        | TION S      | IGNALS           |                  | CODE                 |

|----------------------|---------------------------------------------------------------------------------------------------------------------|------------------|-------------|-------------|------------------|------------------|----------------------|

| F( )                 | FUNCTION                                                                                                            | F16              | F8          | F4          | F2               | F1               | F( )                 |

| 0<br>1<br>2<br>3     | Read Group 1 Register Read Group 2 Register Read and Clear Group 1 Register Read Complement of Group 1 Register     | 0<br>0<br>0      | 0 0 0       | 0 0 0       | 0<br>0<br>1      | 0<br>1<br>0      | 0<br>1<br>2<br>.3    |

| 4<br>5<br>6<br>7     | Non-standard<br>Reserved<br>Non-standard<br>Reserved                                                                | 0 0 0            | 0 0 0 0 0 0 | 1<br>1<br>1 | 0 0 1 1 1        | 0<br>1<br>0      | 4<br>5<br>6<br>7     |

| 8<br>9<br>10<br>11   | Test Look-at-Me<br>Clear Group 1 Register<br>Clear Look-at-Me<br>Clear Group 2 Register                             | 0<br>0<br>0      | 1<br>1<br>1 | 0<br>0<br>0 | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 8<br>9<br>10<br>11   |

| 12<br>13<br>14<br>15 | Non-standard<br>Reserved<br>Non-standard<br>Reserved                                                                | 0 0 0            | 1 1 1       | 1<br>1<br>1 | 0<br>0<br>1<br>1 | 0<br>1<br>0      | 12<br>13<br>14<br>15 |

| 16<br>17<br>18<br>19 | Overwrite Group 1 Register Overwrite Group 2 Register Selective Set Group 1 Register Selective Set Group 2 Register | 1 1 1 1          | 0 0 0       | 0 0         | 0<br>0<br>1      | 0<br>1<br>0<br>1 | 16<br>17<br>18<br>19 |

| 20<br>21<br>22<br>23 | Non-standard Selective Clear Group 1 Register Non-standard Selective Clear Group 2 Register                         | 1<br>1<br>1      | 0<br>0<br>0 | 1<br>1<br>1 | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 20<br>21<br>22<br>23 |

| 24<br>25<br>26<br>27 | Disable Execute Enable Test Status                                                                                  | 1<br>1<br>1<br>1 | 1<br>1<br>1 | 0<br>0<br>0 | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 24<br>25<br>26<br>27 |

| 28<br>29<br>30<br>31 | Non-standard<br>Reserved<br>Non-standard<br>Reserved                                                                | 1<br>1<br>1      | 1<br>1<br>1 | 1<br>1<br>1 | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 28<br>29<br>30<br>31 |

### DATAWAY TIMING '

# PIN ALLOCATION AT NORMAL STATION

(Stations 1-24)

| W24 = most sig   | nificant bit inificant bit         | P1 P2 P3 P4 P5 X I C N L S1 S2 W24 W22 W20 W18 W16 W14 W12 W10 W8 W6 W4 W2 R24 R22 R20 R18 R16 R14 R12 R10 R8 R6 | B<br>F16<br>F8<br>F4<br>F2<br>F1<br>A8<br>A4<br>A2<br>A1<br>Z<br>Q<br>W23<br>W21<br>W19<br>W17<br>W15<br>W13<br>W11<br>W9<br>W7<br>W5<br>W3<br>W1<br>R23<br>R21<br>R19<br>R17<br>R15<br>R13<br>R11<br>R9<br>R7<br>R5 | Busy Function Function Function Function Sub-address Sub-address Sub-address Initialize Response        | Bus-line |

|------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Bus-lines Reserv | / d.c.<br>a.c. Live<br>ved<br>d.c. | R4<br>R2<br>-12<br>+200<br>ACL<br>Y1<br>+12<br>Y2<br>0                                                           | R3<br>R1<br>-24<br>-6<br>ACN<br>E<br>+24<br>+6                                                                                                                                                                       | -24V d.c.<br>-6V d.c.<br>117V a.c. Neutral<br>Clean Earth<br>+24V d.c.<br>+6V d.c.<br>OV (Power Return) | Power<br>Bus-lines                                                                        |

# PIN ALLOCATION AT CONTROL STATION

(Station 25)

| 1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                                                                                                                         |                                                                                                                           |                                                                                                              |                                                                                           |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|