# MODEL 2277 32 CHANNEL CAMAC TDC

## TABLE OF CONTENTS

| Section 1                                                                                                                                                                                     |           |       |                                                               |            |                |                                          |                           |       |                                       |      |     |                            |                                      |                                         |                                               |            |               |       |                |                 |              |                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------|---------------------------------------------------------------|------------|----------------|------------------------------------------|---------------------------|-------|---------------------------------------|------|-----|----------------------------|--------------------------------------|-----------------------------------------|-----------------------------------------------|------------|---------------|-------|----------------|-----------------|--------------|----------------------------------------|

| General Information                                                                                                                                                                           | 2003 D S  |       | 29 <b>4</b> - 23 <b>4</b> - 2                                 | • 9• 9     | 3 <b>.</b> 33. | 79 N                                     | * *                       |       | 04 G                                  | - 12 | 4 9 | · 9                        |                                      | 8                                       | ē iš                                          | ۰          | ٠             |       | ice.           | 8 <b>.</b> 00   |              | 1-1                                    |

| 1.1 Purpose 1.2 Unpacking and Inspection 1.3 Warranty 1.4 Product Assistance 1.5 Maintenance Agreements 1.6 Documentation Discrepancies 1.7 Software Licensing Agreemen 1.8 Service Procedure |           |       |                                                               |            |                |                                          | 3 18<br>* *<br>* *<br>* * |       |                                       |      |     |                            |                                      | # :                                     |                                               |            |               | • •   |                |                 |              | 1-1<br>1-1<br>1-1<br>1-1<br>1-2        |

| Section 2                                                                                                                                                                                     |           |       |                                                               |            |                |                                          |                           |       |                                       |      |     |                            |                                      |                                         |                                               |            |               |       |                |                 |              |                                        |

| Product Description                                                                                                                                                                           | # # # # # | 2 W W | • (5.                                                         |            | 8 8            |                                          | 8.8                       | •     | 9 3                                   |      |     | S* 35                      |                                      | i.                                      | 312                                           | <b>⊙</b> ? | 9 9           | • : • | oxo            | (( <b>.</b> )() |              | 2-1                                    |

| 2.1 Introduction 2.2 Product Description 2.3 Specifications 2.4 Front Panel 2.5 Controls and Connectors 2.6 CAMAC Commands and Fun 2.7 Control Word 2.8 Output Word                           | ctions    |       |                                                               |            |                |                                          |                           |       | * * * * * * * * * * * * * * * * * * * |      |     | # 5<br># 8<br>\$ 3<br>\$ 4 | • 15<br>• 15<br>• 15<br>• 15<br>• 15 |                                         | 4 4<br>3 3<br>4 3<br>4 3                      |            |               |       |                |                 | • • •        | 2-1<br>2-1<br>2-2<br>2-3<br>2-3        |

| Section 3                                                                                                                                                                                     |           |       |                                                               |            |                |                                          |                           |       |                                       |      |     |                            |                                      |                                         |                                               |            |               |       |                |                 |              |                                        |

| Installation                                                                                                                                                                                  |           | · * * |                                                               | s <b>*</b> | ( ¥)           | * *                                      |                           |       | * *                                   |      |     | 2 9                        |                                      | 9                                       | 9 9                                           | <b>(</b> ) | ٠             | • .   | i es           | 10500           | •            | 3-1                                    |

| 3.1 General Installation                                                                                                                                                                      | E E E E   | 1 E E |                                                               |            |                | <br>                                     | 0 0<br>8 8                | * *   |                                       | •    | * : | 2 2                        | • •                                  | 3 <b>•</b> :                            | 3 /4<br>3 (4                                  |            | ****<br>***** | •20°• | 80 <b>0</b> 10 | 2 <b>4</b> 17   | ncat<br>Otio | 3-1<br>3-1                             |

| Section 4                                                                                                                                                                                     |           |       |                                                               |            |                |                                          |                           |       |                                       |      |     |                            |                                      |                                         |                                               |            |               |       |                |                 |              |                                        |

| Operating Instructions                                                                                                                                                                        | e e e e   | E 6 9 |                                                               |            |                | ź.                                       | 2. 2.                     |       | 2.5                                   |      |     | * 9                        |                                      | ::                                      |                                               | 0.00       | 3 <b>4</b> 55 |       |                | 200             | 818          | 4-1                                    |

| 4.1 General Operation 4.2 Common Start vs. Common S 4.3 Pulse vs. Latch Modes 4.4 Front Panel Control Signal Inp 4.5 Front Panel Outputs 4.6 Reading the Data 4.7 Daisy Chaining the 2277     | top M     | odes  | n e e<br>Till till<br>Till till till till till till till till |            |                | * * *<br>* *<br>* *<br>* *<br>* *<br>* * |                           | * * * |                                       |      |     | # 9<br>* 4<br>* 9<br>* 9   |                                      | % : : : : : : : : : : : : : : : : : : : | 6 6<br>9 6<br>9 9<br>9 9<br>9 9<br>9 9<br>8 0 |            |               |       |                |                 |              | 4-1<br>4-3<br>4-4<br>4-5<br>4-6<br>4-6 |

| 4.8 Internal Tester 4.9 Testing the 2277 using the Inte 4.10 Testing the 2277 Using the Te                                                                                                    | mai i     | PCLET |                                                               |            |                |                                          |                           |       |                                       |      |     |                            |                                      |                                         |                                               |            |               |       |                |                 |              | 4                                      |

# TABLE OF CONTENTS [continued]

| Section 5                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------|

| Theory of Operation                                                                                                         |

| 5.1 Gray Code Counter Coarse Time Measurement                                                                               |

| 5.2 Asynchronous Delay Line Time Interpolation 5-1                                                                          |

| 5.3 Common Input Latch       5-1         5.4 Leading and Trailing Edge Detection       5-1         5.5 Test Input       5-1 |

| 5.4 Leading and Trailing Edge Detection                                                                                     |

| 5 5 Test Input                                                                                                              |

| 5.6 Data Processor                                                                                                          |

| 5.7 Read Only Memory Channel Number Encoding 5-2                                                                            |

| 5.7 Read Only Memory Channel Funder Encoding                                                                                |

| 5.8 Sparse Data Priority Readout System                                                                                     |

| 5.9 Wire-ORed Trigger Outputs 5-2                                                                                           |

| 5.10 Readout Data Processor                                                                                                 |

| 5.10 Readout Data Processor                                                                                                 |

| n a                                                                                                                         |

| Section 6                                                                                                                   |

| Schematics and Parts List                                                                                                   |

|                                                                                                                             |

| —————————————————————————————————————                                                                                       |

| Index                                                                                                                       |

## LIST OF FIGURES

|       | 2277 Front Panel - Not drawn to size                       |                                             |           |               |                       |          |       |       |

|-------|------------------------------------------------------------|---------------------------------------------|-----------|---------------|-----------------------|----------|-------|-------|

| 4-1.  | 2277 General Operation Flowchart                           |                                             |           |               |                       | :        |       | . 4-2 |

| 4-2.  | An example of proper signal timing for operation in Comi   | mon Stop                                    | Mode.     |               |                       |          |       | . 4-4 |

| 4-3.  | An example of proper signal timing for operation in Comi   | mon Start                                   | Mode.     |               | 11.3                  | 10       |       | . 4-4 |

|       | Example of timing relationship between hits and the trigge |                                             |           |               |                       |          |       |       |

| La    | tch Mode                                                   | * * * * * * *                               | 0.0.0.2   |               |                       | 9        |       | . 4-5 |

| 4-5.  | Example of timing relationship between hits and the trigge | er outputs                                  | when      | operati       | ng i                  | n        |       |       |

| Pu    | lse Mode                                                   | $\star \star \star \star \star \star \star$ | * * * *   | * * * * *     | 9 9 9                 | • (0.)   | *100  | . 4-5 |

| 4-6.  | ECL Terminations                                           | *****                                       | * * * *   | 3 3 3 3 3     |                       | • •      | • •   | . 4-5 |

| 4-7.  | Front Panel COM Input Termination Network                  |                                             |           |               | • (•)                 | • •      | • •   | . 4-7 |

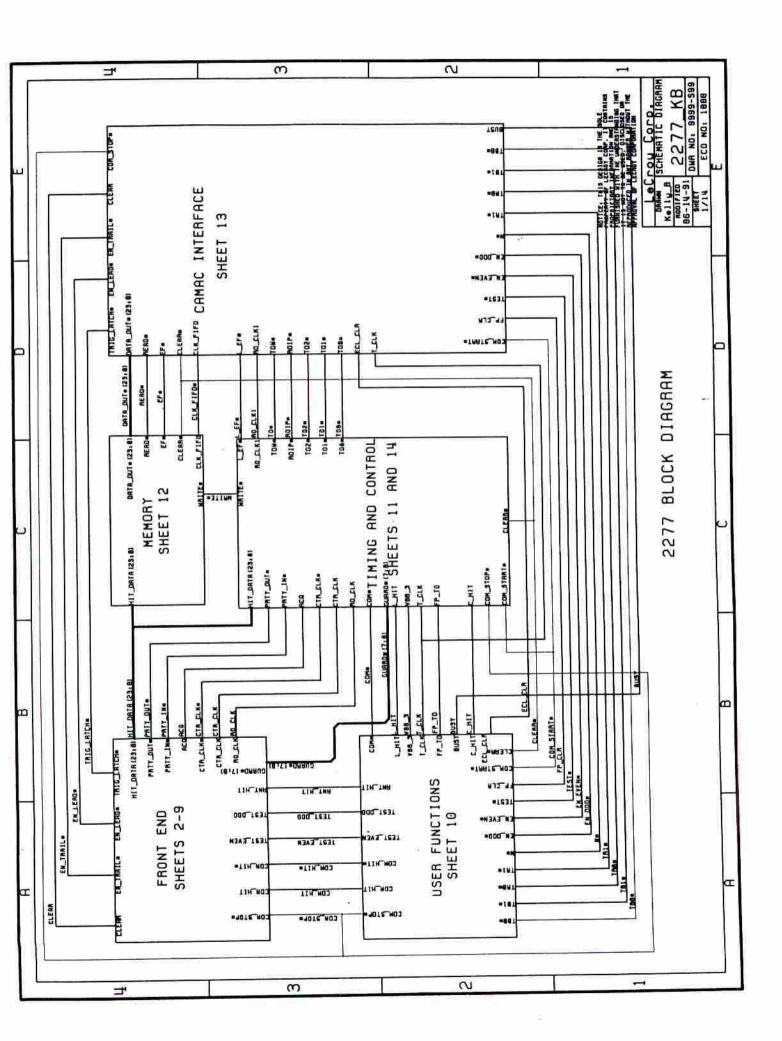

| 6-1.  | 2277 Block Diagram                                         | *****                                       | 8 9 9 8   | 6.6.6.6       |                       | •        | •     | . 6-1 |

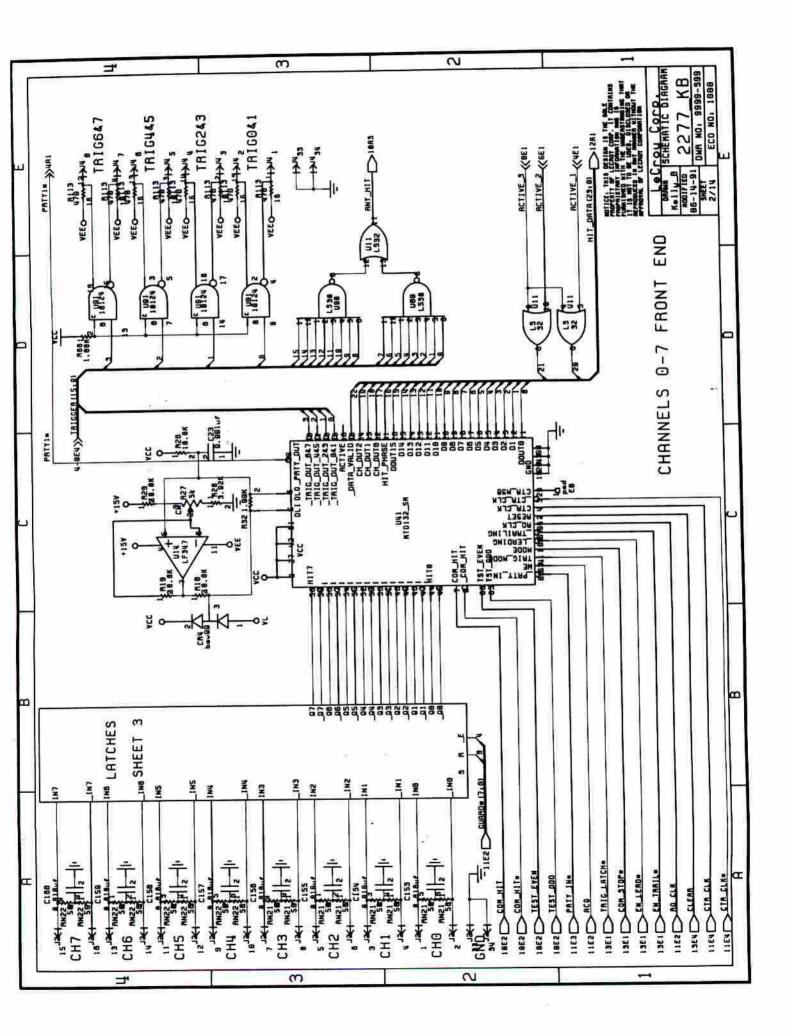

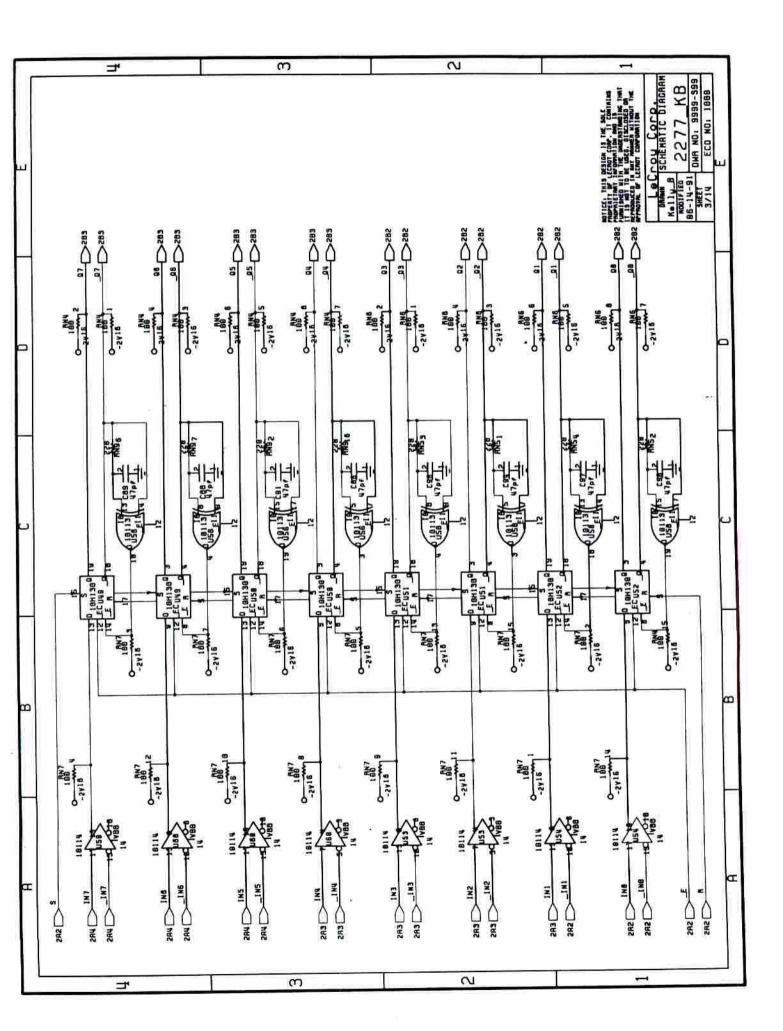

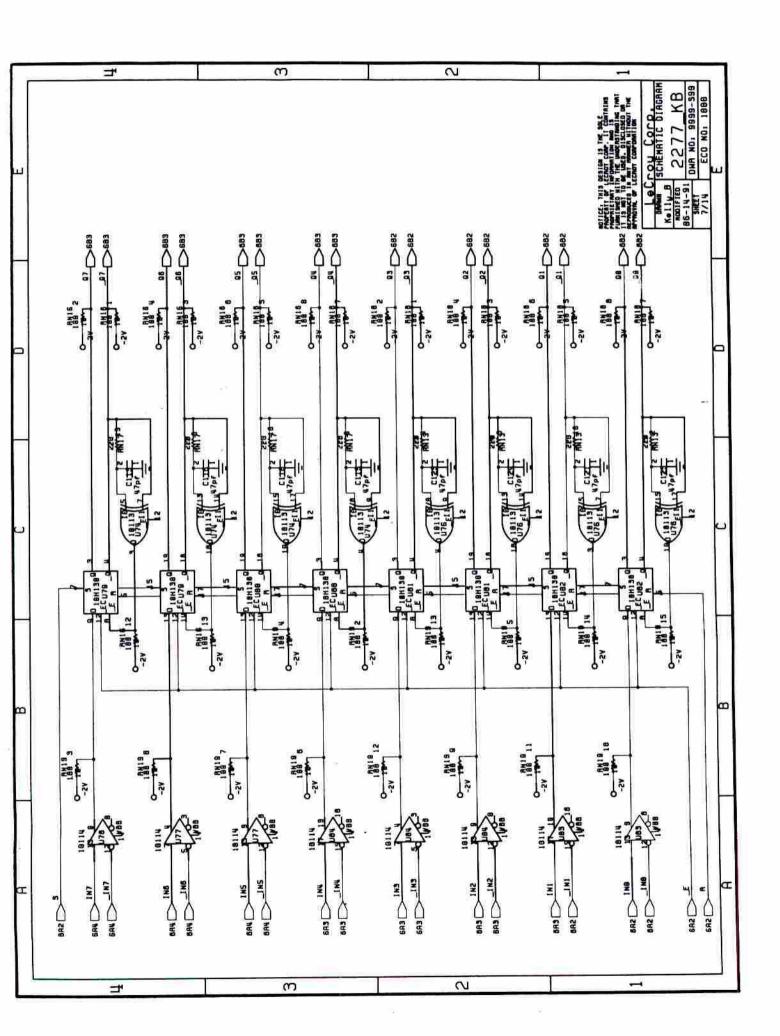

|       | 2277 Channels 0-7 Front End                                |                                             |           |               |                       |          |       |       |

| 6-3.  | 2277 Front End Guard                                       | * * * * * * *                               | ****      | 9 30333       |                       | •        |       | . 6-5 |

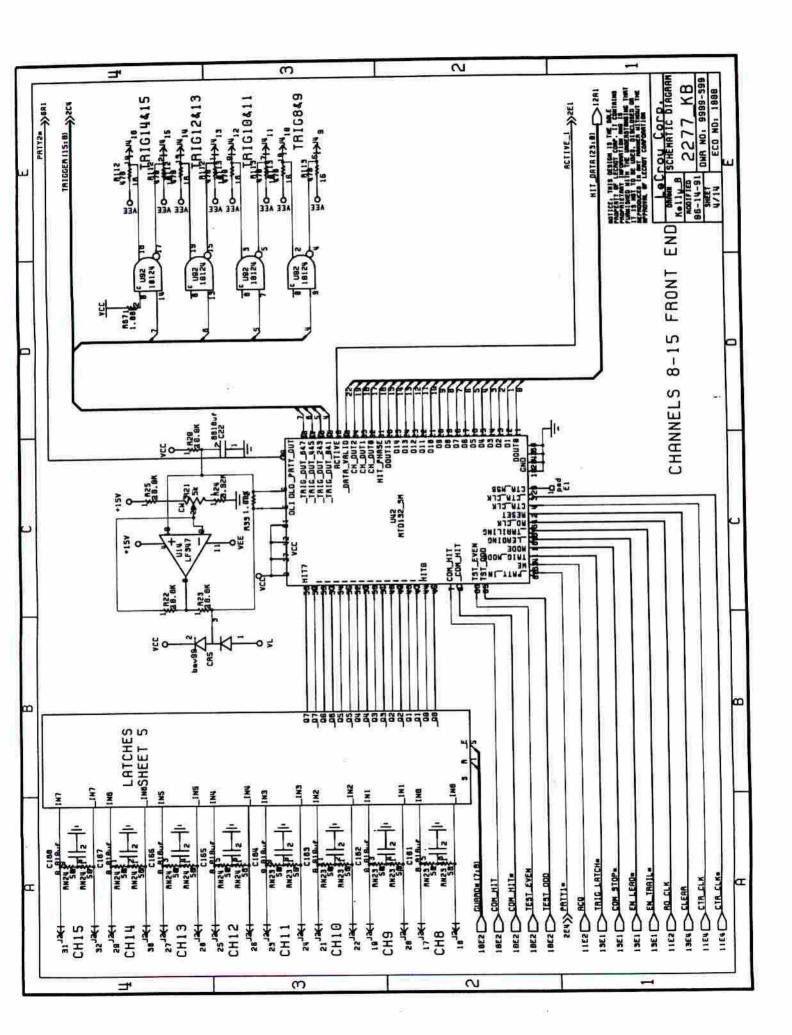

| 6-4.  | 2277 Channels 8-15 Front End                               | 333334                                      | 111111    |               | • •                   | 6.6      | 88    | . 6-7 |

| 6-5.  | 2277 Front End Guard                                       | *****                                       | 4.500     |               | 61.00                 | 40 40    | 40.00 | . 6-9 |

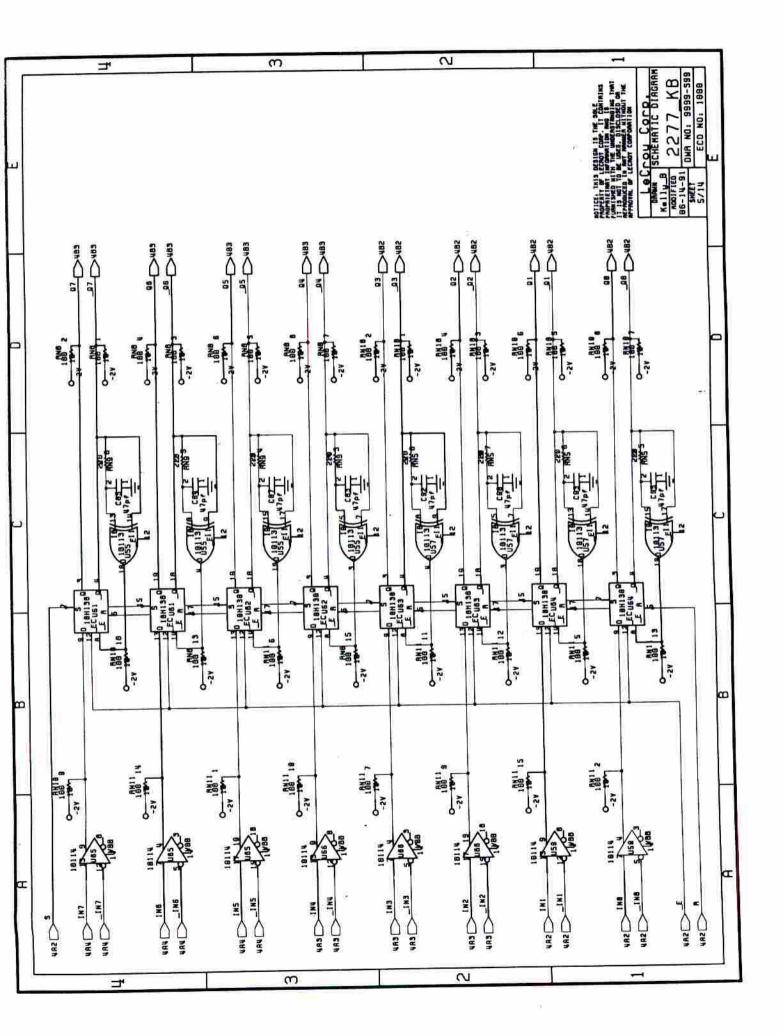

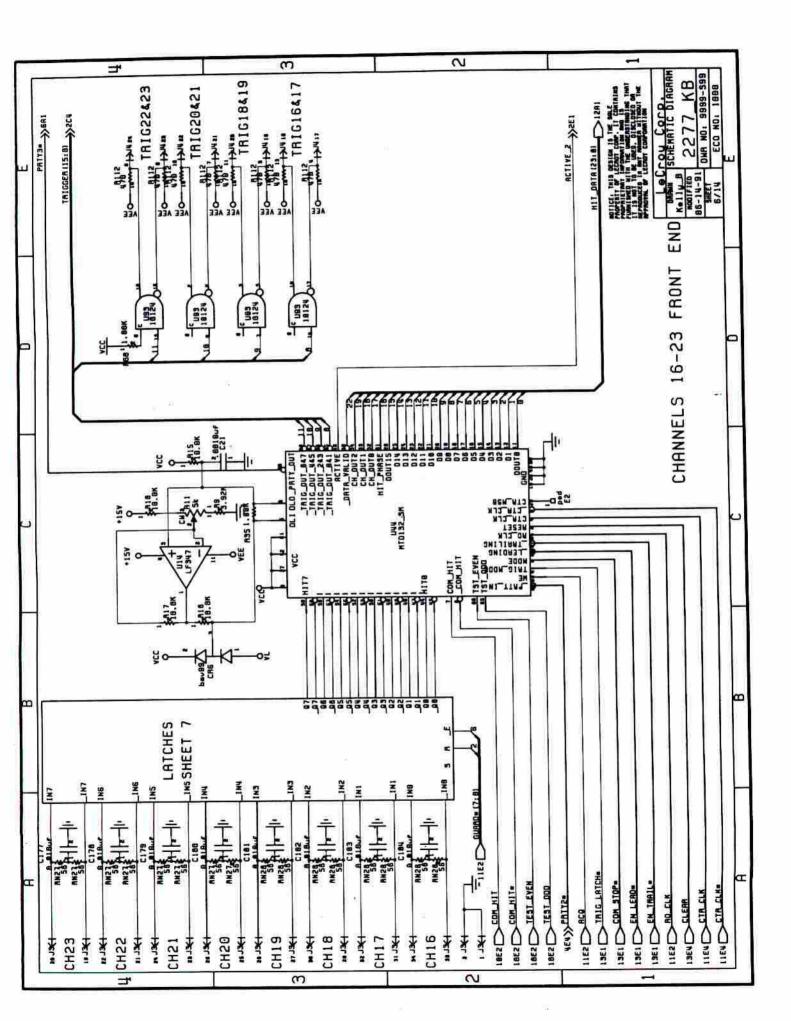

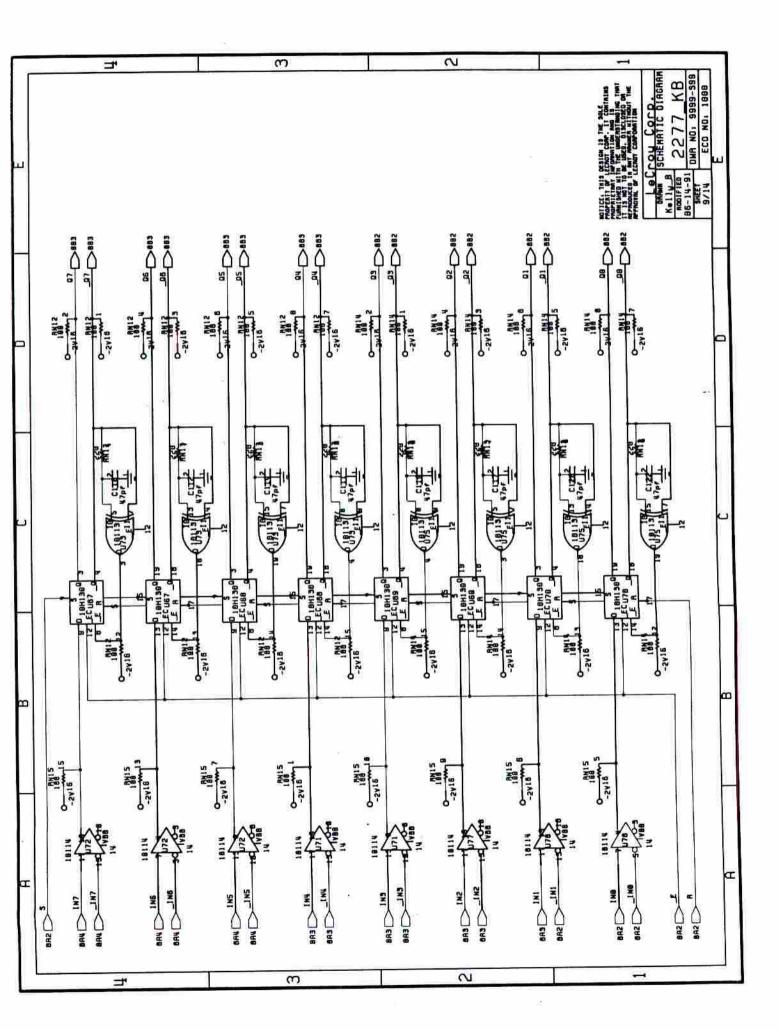

| 6-6.  | 2277 Channels 16-23 Front End                              | 34 34 34 34 34 34                           |           |               | <b>6</b> 8            | <u> </u> | *) *: | 6-11  |

| 6-7.  | 2277 Front End Guard                                       |                                             |           |               | 16.55                 | 16 to    | to to | 6-13  |

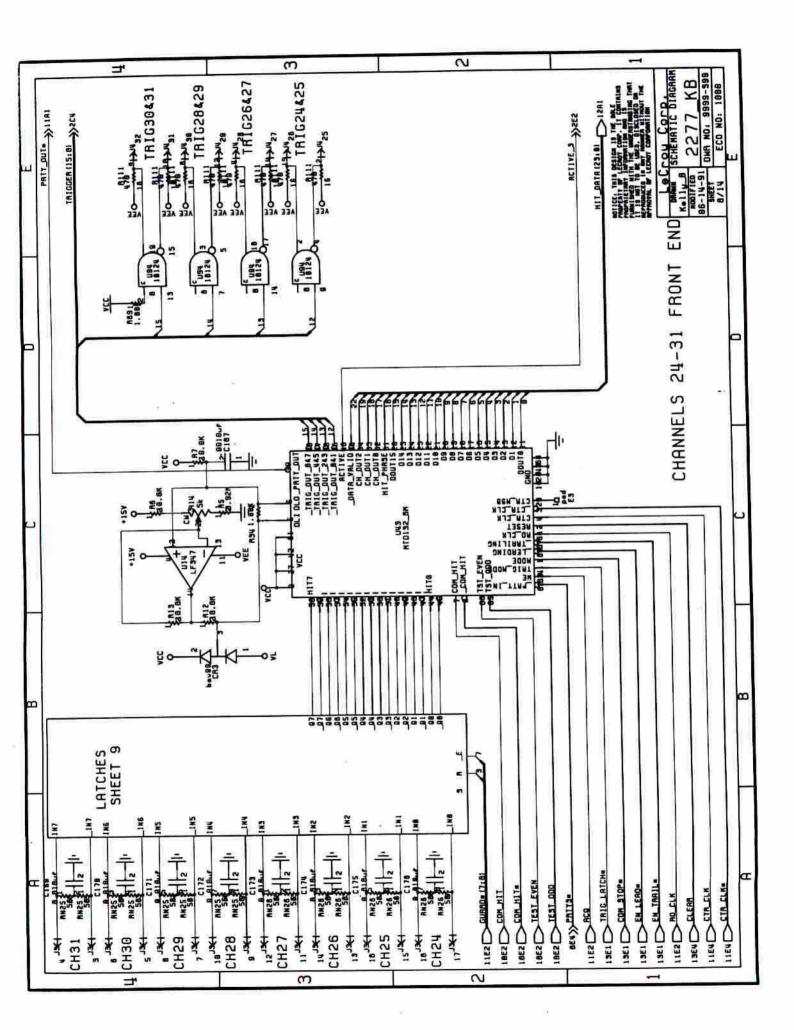

| 6-8.  | 2277 Channels 24-31 Front End                              |                                             |           | www.e.s       | 8.2                   | 2 2      | 2 2   | 6-15  |

| 6-9.  | 2277 Front End Guard                                       | A 4 3 35 656                                |           |               | <b>*</b> 3 <b>*</b> 3 | * *      | * *   | 6-17  |

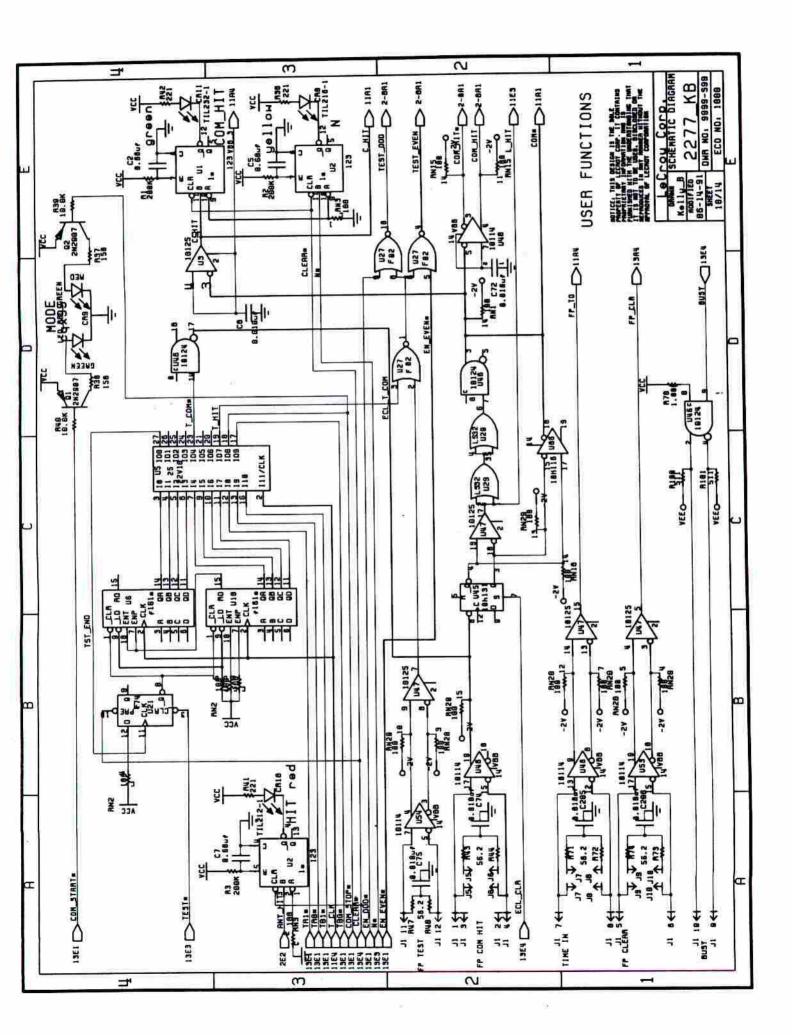

| 6-10. | 2277 User Functions                                        | 3 0 00000000                                | nemente k | 5 50 50 50 50 | 50 50                 |          |       | 6-19  |

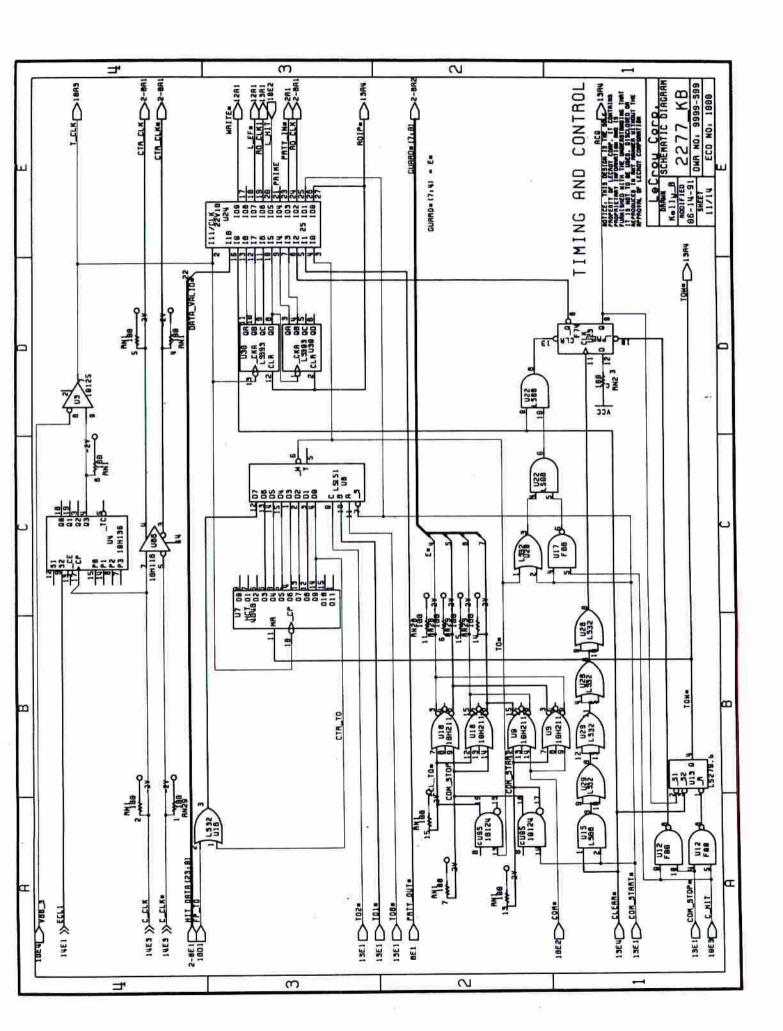

| 6-11. | 2277 Timing Control                                        |                                             | £ 6 5 5   |               | 88                    | •        |       | 6-21  |

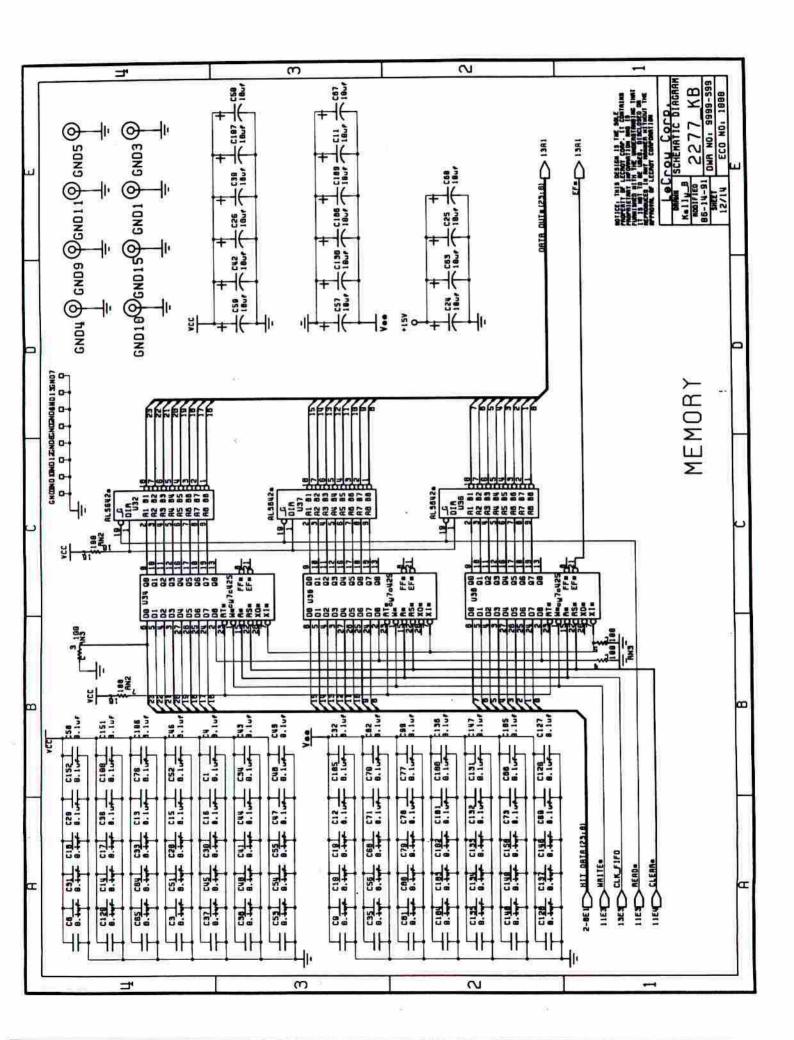

|       | 2277 Memory                                                |                                             |           |               |                       |          |       |       |

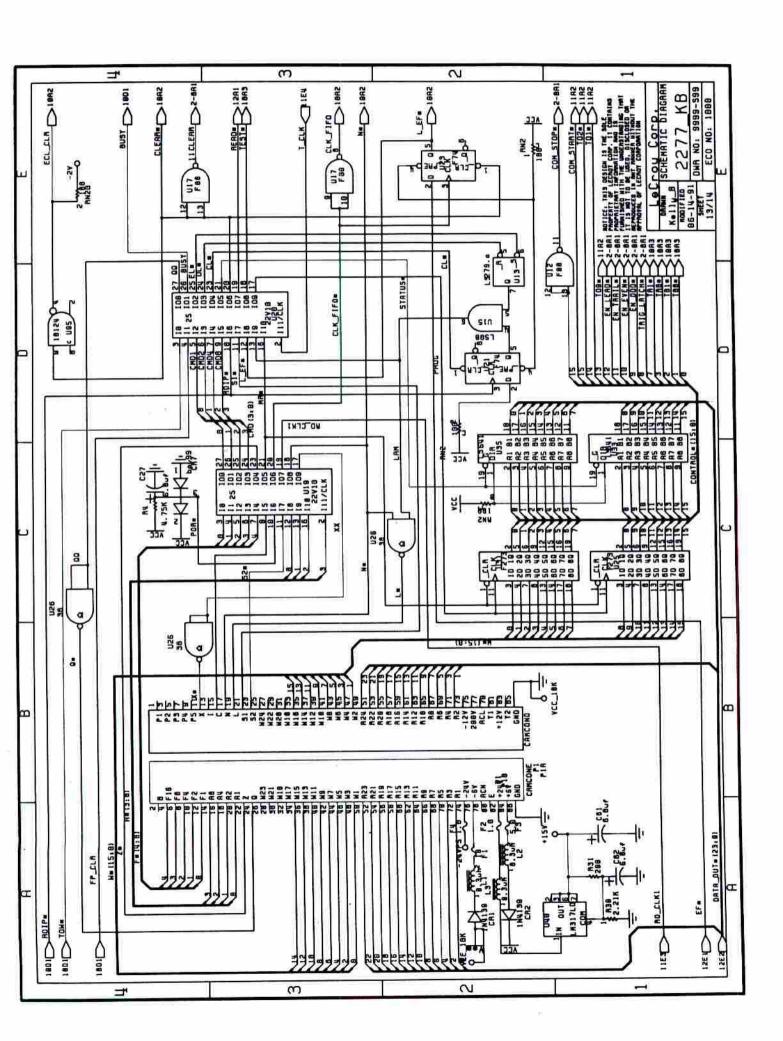

| 6-13. | 2277 CAMAC Interface                                       | 000000000000000000000000000000000000000     |           | * * * * *     | * *                   |          |       |       |

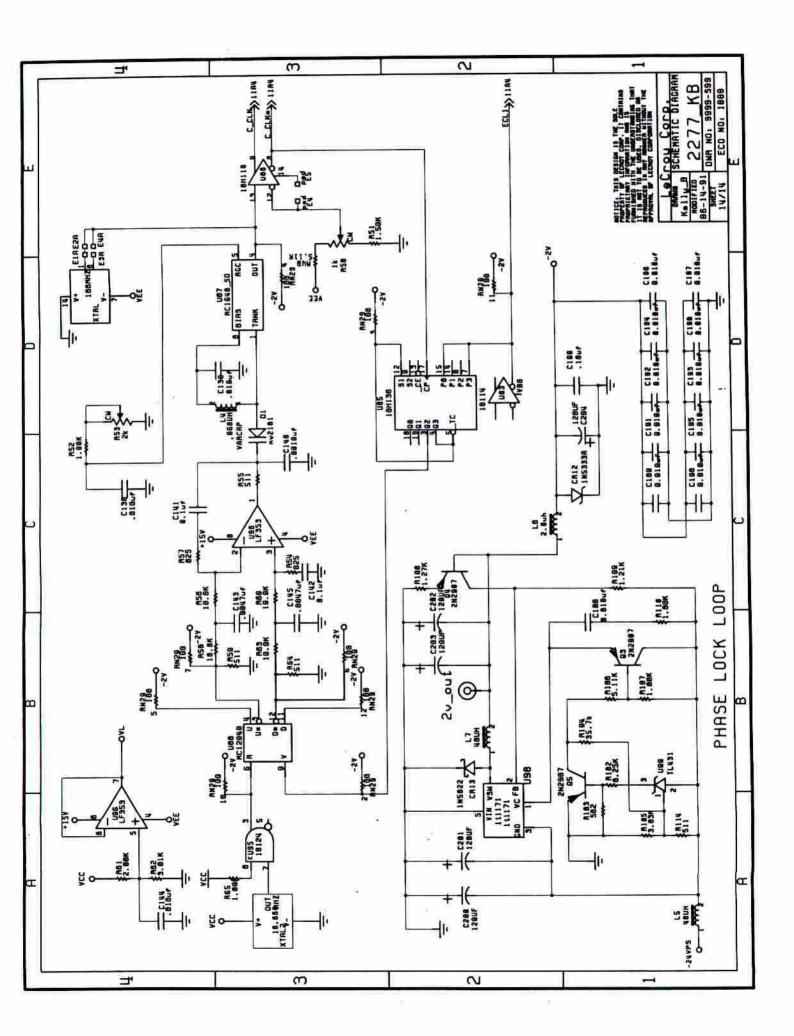

| 6-14. | 2277 Counter Clock Generation                              |                                             |           |               |                       |          | * *   | 6-27  |

# LIST OF TABLES

| 2-1. | Status Word Definition Output Data Word Definition | 200 |

|------|----------------------------------------------------|-----|

| 2-2  | Output Data Word Definition                        | 2-1 |

|      | Output Data Word Definition                        | 2-  |

# **CAUTION**

## Cooling

It is imperative that the module 2277 TDC be well cooled. Be sure fans move sufficient air to maintain exhaust air temperature at less than 50 C.

#### Installation

Crate power should be turned off during insertion or removal of modules in accordance with the CAMAC specification.//

## Specifications

The information contained in this manual is subject to change without notice. The reference for product specification is the Technical Data Sheet effective at the time of purchase.

# Electrostatic Sensitivity

While measures have been taken to protect the MTD132 ASIC from electrostatic damage, it is still imperative to follow antistatic procedures when handling this CMOS device Removal of the MTD132 from its socket may void the warranty.

# CAUTION

## 2277 DIGITAL COUNTER TIME-TO-DIGITAL CONVERTER

TDCs FOR HIGH RATE EXPERIMENTS

- 1 nsec LSB

- 16-Bit Range, 64 µsec Full Scale

- 32 Channels Per CAMAC Module

- Common START or STOP

- Multihit Capability, 16

Measurements (Hits)/Channel

- Leading and/or Trailing Edge, Allows Pulse Width Measurements

- 20 nsec Double Edge Resolution

- Zero Pedestal

- Chip Level Zero Suppression

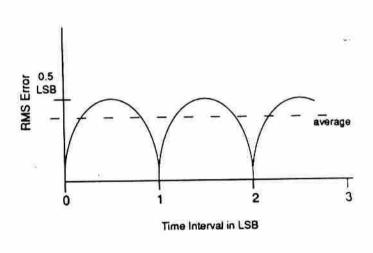

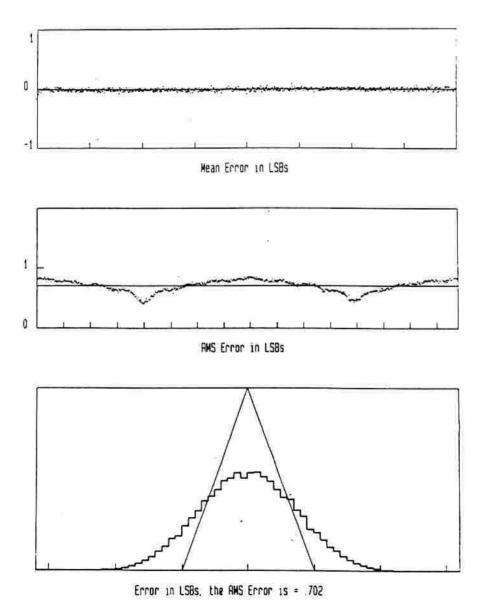

The 32-channel, CAMAC-based Model 2277 Digital Counter Time-to-Digital Converter (TDC) has been designed for a wide variety of timing applications. The module features a 16-bit dynamic range, 1 nsec LSB (750 psec R.M.S.) and a 16 element pipeline. The double edge resolution is below 20 nsec. The module is ideal for time measurements of drift chambers, time projection chambers or other detectors requiring time interval measurements with high accuracy.

The Model 2277 can be operated in either a COMMON STOP or COMMON START mode. At the end of the acquisition period, the time elapsed between each hit and the COMMON STOP or START along with the address of the associated channel may be read out via CAMAC. The data is automatically zero suppressed. A trigger port with prompt outputs is also provided.

Corporate Headquarters: 700 Chestnut Ridge Road, Chestnut Ridge, NY 10977-6499, USA. Tel: (914) 425-2000 TWX: 710-577-2832

.

1

## **FUNCTIONAL DESCRIPTION**

The Model 2277 Digital Counter TDC is a CAMAC instrument for the measurement of multiple time intervals, accurate to 1 nanosecond for time ranges greater than 64 microseconds//

The times are measured with respect to a common reference time mark or "COMMON HIT", which can occur/before)or(after)the individual time signal (also called "HIT") inputs to be measured. This common reference concept is appropriate when the relative times between one input channel) and any other input channel) is of interest, since they are both measured with respect to a common time. It is also appropriate for absolute time measurements between the individual signal inputs and the reference itself.

Because many experiments will need many time measurements, the 2277 has incorporated a large number of independent signal channels (however, single measurements are just as appropriate). In addition, each individual input channel has a FIFO type buffer attached to it such that up to 16 hits can be recorded on the channel with respect to the common hit.

The 2277 inputs are an edge sensitive design./Consequently the polarity of the logic signal inputs is selectable./The module will record the time of the rising, falling, or both signal edges.//

#### Common Start and Common Stop Modes

When the common reference time precedes the signal times/the 2277 is operating in a "COMMON START" mode/Alternatively, if the inputs precede the reference the "COMMON STOP" mode is used/Of course, by adding delays to the common or individual signals either mode can be used//

Common start mode is typically preferred in synchronous situations, such as colliding beam accelerators or pulsed laser experiments, when the time interval to be measured can be associated in time with a causal effect, In common start mode, a time window for the measurements must also be provided to terminate the measuring process, This can be internally generated in the 2277 or supplied from an external source via a front-panel input).

Common stop mode is better suited to continuous beam) or (randomly occurring events) when a trigger decision is required//

#### Operation of the TDC

The 2277 must be configured and operated from CAMAC //The configuration of the module is determined by the status register //The data value stored in the register is decoded as a bit pattern (see Table 1) // The bit pattern permits the mode selection / internal time window duration, edge sensitivity / test features and trigger output type // Once the status register is configured time measurement can be made //

The actual measurements are a combination of front panel signals and CAMAC commands. A typical operation sequence begins with a CAMAC Clear command or pulse on the CLR input. This readies the module for data taking. The registration of individual hits and common hits begins automatically. At the completion of the measurement, (a time-out in common start mode from the internal timer or front-panel T-IN input, or the arrival of a hit in common stop mode) the embedded data processor takes over/This processor primarily does two things./It combines the individual hit marks and the common mark to produce the time data desired, and it suppresses data which results in a zero or overflow condition/The accumulated data is passed to a readout FIFO in the 2277//During this process/a BUSY signal is output from the front panel. The busy condition can also be monitored by CAMAC.

The data can now be read through CAMAC to the host computer. Readout is accomplished with a single CAMAC function code. The channel number associated with each data value is passed along with it. In fact, readout can begin as soon as the embedded processor has transferred the first word into the 2277 readout FIFO. In this way, "conversion" time and data transfer time can overlap, resulting in reduced dead-time and increased data throughput. The readout is complete when both Busy and CAMAC Q are returned as zero.

If for some reason the data is not read, it can be cleared. This restarts the data acquisition cycle again.

#### **Test Features**

The 2277 contains an internal pulse generator so that signals can be <u>injected</u> to <u>verify</u> the behavior of each channel./The internal tester is controlled by the status register//In addition, there is a front panel TEST input so an external pulse generator can be used./

#### Additional Features and Applications

Prompt hit information is presented at the front panel TRIG PAIR OUT port for inclusion in first level trigger decisions./The input channels are paired and OR'd together./A hit on either channel of the pair produces a pulse or latched output bit./These outputs are designed to match the LeCroy ECLine programmable trigger logic standard.//

By capturing both the leading and trailing edge time information/the 2277 can be used in a time-over-threshold technique to simultaneously determine time and charge from a given detector element//This low cost technique avoids many of the traditional problems of using ADCs and TDCs together.//

This TDC is based on the LeCroy MTD132A Monolithic Time Digitizer chip//The 2277 is essentially identical to the Model 1177 VME TDC and is similar to the Model 1877 FASTBUS TDC For this reason the 2277 is an ideal testbed for chamber developments.

# SPECIFICATIONS

#### **GENERAL**

Channels: 32, differential ECL inputs. Impedance 112  $\Omega$ . Unused inputs/outputs are allowed to float. COMMON START/STOP: Front-panel ECL 2-pin connectors; 112  $\Omega$  terminating resistors.

Range: 16 bits.

Full Scale: 65.535 µsec.

Sensitivity (Resolution): 1 nsec least count,

(750 psec R.M.S.).

Double Edge Resolution: < 20 nsec. Long Term Stability: 10 ppm/year. Integral Non-Linearity: None (0%). Differential Non-Linearity: <±20%.

Digital Clear: 100 nsec.

Buffering: 4.3 µsec + 533 nsec per hit.

Data Format: 16 bits data, 1 bit edge polarity, 5 bits

channel address.

Power: -24 V at < 25 A; -6 V at < 2 A; +6 V at < 1 A;

+24 V at < 20 mA.

Mechanical: #1 CAMAC Module according to IEEE-

583 Standard.

Weight: 1.5 lbs. (0.7 kg).

#### FRONT PANEL LEDS

N٠

Red LED indicates accessing

module.

MODE:

Bicolor LED. Green indicates COMMON START. Red indicates COMMON STOP.

HIT:

Yellow LED indicates whether any channel received a hit.

COM HIT:

Green LED indicates whether a COMMON START/STOP was

received.

#### INPUT SIGNALS

All inputs are differential ECL signal standard.

IN 0-31:

32 channel inputs.

COM:

2 bridged connectors.

CLR:

Clear; resets module - aborts

conversion.

T-IN:

TEST:

Time out: terminates COMMON

START acquisition window.

the odd and even numbered

Used to provide test pulses to

**OUTPUT SIGNALS**

TRIG PAIR OUT:

16 outputs - pairwise OR'd

channels.

BUSY:

Indicates front end disabled due

to buffering and readout.

## CAMAC COMMANDS

F(0)-A(0):

Read Data. Q = 1 if valid data.

Q = 0 if FIFO is empty.

F(25)·A(0):

Test Cycle.

F(1).A(0):

Read Status Register.

Write Status Register.

F(26)•A(0):

Enable LAM.

F(8)-A(0):

Test LAM. Q = 1 if LAM is set.

F(27)•A(0):

Test "Buffering in Progress".

Q = 1 if true.

F(9)·A(0):

Clear. F(9) does not affect

status register.

F(27)·A(1):

Notes

Test Busy. Q = 1 if Busy is true.

F(10)+A(0):

Clear LAM.

channels.

1. Any CAMAC command must be accompanied by a valid N (Station Number).

F(17)-A(0): F(24)-A(0):

Disable LAM.

An X = 1 response is generated for any valid CAMAC command.

#### STATUS REGISTER BIT CONFIGURATIONS

| BIT(S)                   | CONTROL FUNCTION            | PATTERN | VALUE        |

|--------------------------|-----------------------------|---------|--------------|

| 16                       | MODE                        | Ö       | COMMON STOP  |

|                          |                             | ì       | COMMON START |

| 15, 14, 13<br>Controlled | COMMON START TIMEOUT        | 000     | Front Panel  |

|                          |                             | 001     | 1024 nsec    |

|                          |                             | 010     | 2048 nsec    |

|                          |                             | 011     | 4096 nsec    |

|                          |                             | 100     | 8192 nsec    |

|                          |                             | 101     | 16384 nsec   |

|                          |                             | 110     | 32768 nsec   |

|                          |                             | 111     | 65536 nsec   |

| 12                       | HIT LEADING EDGE RECORDING  | 0       | DISABLE      |

|                          |                             | 1       | ENABLE       |

| 11                       | HIT TRAILING EDGE RECORDING | 0       | DISABLE      |

|                          |                             | ī       | ENABLE       |

| 10                       | EVEN CHANNEL TEST INPUT     | 0       | DISABLE      |

|                          |                             | ĭ       | ENABLE       |

| 9                        | ODD CHANNEL TEST INPUT      | 0       | DISABLE      |

|                          |                             | 1       | ENABLE       |

| 8                        | TRIGGER MODE                | 0       | PULSE        |

|                          |                             | 1       | LATCH        |

| 4, 3                     | TESTER HIT DURATION         | 00      | 128 nsec     |

|                          |                             | 01      | 256 nsec     |

|                          |                             | 10      | 1024 nsec    |

|                          |                             | 11      | 2048 nsec    |

| 2, 1                     | TESTER HIT BURST            | 00      | 1 hit        |

|                          |                             | 01      | 2 hits       |

|                          | a a                         | 10      | 4 hits       |

|                          |                             | 11      | 8 hits       |

4

a .

\_

.

# General Information

## 1.1 Purpose

This manual is intended to provide instruction regarding the setup and operation of the LeCroy Model 2277 Time to Digital Converter/In addition, it describes the converter's theory of operation and presents information regarding its function and application/

## 1.2 Unpacking and Inspection

It is recommended that the <u>shipment</u> be thoroughly inspected immediately upon delivery//All material in the container should be checked against the enclosed Packing List and shortages reported promptly//If the shipment is damaged in any way, please notify the Customer Service Department or the local field service office//If the damage is due to mishandling during shipment/you may be requested to assist in contacting the carrier in filing a damage claim//

### 1.3 Warranty

LeCroy warrants its instrument products to operate within specifications under normal use and service for a period of one year from the date of shipment Component products, replacement parts, and repairs are warranted for 90 days This warranty extends only to the original purchaser Software is thoroughly tested, but is supplied "as is" with no warranty of any kind covering detailed performance Accessory products not manufactured by LeCroy are covered by the original equipment manufacturers warranty only.

In exercising this warranty, LeCroy will repair or, at its option, replace any product returned to the Customer Service Department or an authorized service facility within the warranty period, provided that the warrantor's examination discloses that the product is defective due to workmanship or materials and has not been caused by misuse, neglect, accident or abnormal conditions or operations.

The purchaser is responsible for the transportation and insurance charges arising from the return of products to the servicing facility. LeCroy will return all in-warranty products with transportation prepaid.

This warranty is in lieu of all other warranties, express or implied, including but not limited to any implied warranty of merchantability, fitness, or adequacy for any particular purpose or use. LeCroy shall not be liable for any special, incidental, or consequential damages, whether in contract, or otherwise.

#### 1.4 Product Assistance

Answers to questions concerning installation, calibration, and use of LeCroy equipment are available from the Customer Service Department, 700 Chestnut Ridge Road, Chestnut Ridge, New York, 10977-6499, (914) 578-6030, or your local field service office.

# 1.5 Maintenance Agreements

LeCroy offers a selection of customer support services. For example, Maintenance Agreements provide extended warranty that allows the customer to budget maintenance costs after the initial warranty has expired. Other services such as installation, training, on-site repair, and addition of engineering improvements are available through specific Supplemental Support Agreements. Please contact the Customer Service Department or the local field service office for details.

#### General Information

# 1.6 Documentation Discrepancies

LeCroy is committed to providing state-of-the-art instrumentation and is continually refining and improving the performance of its products. While physical modifications can be implemented quite rapidly, the corrected documentation frequently requires more time to produce. Consequently, this manual may not agree in every detail with the accompanying product and the schematics in the Service Documentation. There may be small discrepancies in the values of components for the purposes of pulse shape, timing, offset, etc., and, occasionally, minor logic changes. Where any such inconsistencies exist, please be assured that the unit is correct and incorporates the most up-to-date circuitry.

# 1.7 Software Licensing Agreement

Software products are licensed for a single machine. Under this license you may:

- Copy the software for backup or modification purposes in support of your use of the software on a single machine.

- Modify the software and/or merge it into another program for your use on a single machine.

- Transfer the software and the license to another party if the other party accepts the terms of this agreement and you relinquish all copies, whether in printed or machine readable form, including all modified or merged versions.

#### 1.8 Service Procedure

Products requiring maintenance should be returned to the Customer Service Department or authorized service facility. If under warranty, LeCroy will repair or replace the product at no charge. The purchaser is only responsible for the transportation charges arising from return of the goods to the service facility. For all LeCroy products in need of repair after the warranty period, the customer must provide a Purchase Order Number before any inoperative equipment can be repaired or replaced. The customer will be billed for the parts and labor for the repair as well as for shipping. All products returned for repair should be identified by the model and serial numbers and include a description of the defect or failure, name and phone number of the user. In the case of products returned, a Return Authorization Number is required and may be obtained by contacting the Customer Service Department in your area.

# **Product Description**

#### 2.1 Introduction

The LeCroy Model 2277 provides 32 channels of either common start or (common stop) multihit Time to Digital Conversion designed for elementary particle or nuclear physics experiments // All input time signals to be measured ('hits') are received via differential ECL (dECL) front panel inputs // Each channel exhibits 1 nsec resolution (LSB) and can store up to 16 hits within a 65 µsec range // The time measurement is performed using the MTD132, a full custom ASIC developed by LeCroy Corporation //

### 2.2 Product Description

The 2277 can be programmed to operate in either common start or common stop mode. When operating in Common Start Mode, a hit window is necessary. This window of up to one full scale may be controlled via the front panel or by programming three bits within the control register. If none is provided, the hit window defaults to full scale or 65 µsec. See sections 4.2 and 4.4 for further details regarding common start and common stop modes.

Each 2277 has 32 channels of front panel inputs and a common input All inputs are dECL and are terminated by an impedance matching network Each channel can store up to 16 hits and can be programmed to detect leading and/or trailing edges Selected edges can be detected with as little as 20 nsec of time separating them. If more than 16 hits occur per channel, the last 16 hits are retained. Two common inputs exist for easy board to board distribution using a "daisy chain connection".

Readout can occur as quickly as 5.12 µs after the end of acquisition. Acquisition ends with either a common stop pulse) or (a timeout) for common stop) and (common start modes) respectively. The MTD 132s inherently sparsify the data, so time is not wasted reading out empty channels. The data of the 2277 is readout as a 22 bit word. The least significant 16 bits are the data; the next bit is the hit phase (denoting leading or trailing edge); and the next 5 most significant bits are the channel information.

Trigger outputs are provided on the front panel in dECL/For trigger purposes only,/the input pulses are pairwise OR'ed (0 & 1, 2 & 3, etc.)//

The functionality of the 2277 can be tested using either an internal tester or a front panel dECL test input)/The internal tester can be programmed to produce 1, 2, 4 or 8 pulses with durations of 128, 256, 1,024, or 2,048 nsecs/Either or both edges of the pulses are selectable for detection, creating up to 16 internal hits per channel//Internal tester hits may be applied to odd and/or even channels simultaneously//Channels may also be tested by supplying pulses via the TEST front panel input and selecting odd and/or even channels by programming the status register accordingly//Testing can be performed in both/Common Start) and/Common Stop Modes.

# 2.3 Specifications

Please refer to the model 2277 technical data sheet for a complete summary of all relevant specifications//

## Product Description

## 2.4 Front Panel

Below is a picture of the front panel of the Module 2277 TDC

Figure 2-1 2277 Front Panel - Not drawn to size.

#### 2.5 Controls and Connectors

Four LEDs on the front panel of the 2277 indicate status of operation / The first is the N LED / It flashes red when the module is addressed via CAMAC / The second is a bi-colored mode LED / If colored green the module is in a Common Start Mode / and if colored red it is in a Common Stop Mode / The third LED flashes yellow if a pulse (HIT) is detected on any of the 32 channels) or (the TEST input // The final LED flashes green when a COMMON HIT (ie. start or stop) occurs //

The first header, or the upper most five inputs, receives the control signals for the board/For further explanation of the front panel control signals see section 4.4./The next two headers marked IN receive the hit inputs//The first sixteen hit inputs are numbered in ascending order from 0 to 15, while the last sixteen hit inputs are numbered in descending order from 31 to 16//The bottom pair of pins on the first header and the top pair of pins on the next header should be properly grounded//The final front panel header marked TRIG PAIR OUT provides signals for triggering purposes and is numbered in ascending order from 1 to 16//The bottom pair of pins on the TRIG PAIR OUT header should be properly grounded//All front panel inputs and outputs are briefly described below//

- COM://A dECL input used to receive the common hit//The leading edge of the signal is latched// Two inputs and socketed terminators are present to aid in daisy chaining boards together//See section 4.7 for further information on daisy chaining the 2277//

- CLR:/A dECL input used to clear the board//The on board memory is cleared, but the control

word maintains its integrity//The board is ready to accept hits 60 nsec after the trailing edge of

the clear pulse which must have a width of at least 20 nsec//

- T-IN://A dECL input used to receive the common start timeout //The trailing edge of the timeout marks the end of acquisition in Common Start Mode//If the front panel common start timeout does not end within 65 μsec after the leading edge of the common hit (start) pulse,/the 2277 is automatically disabled.//

- BUSY://A dECL output which indicates when the front\_end is prohibited from accepting hits.//

The 2277 will not register hits while BUSY is true.//

- TEST:/A dECL input used to aid in test and calibration by providing a test hit to the even and/or odd channels at one time, depending on the status of the control register//The 2277 can be programmed to latch the leading and/or the trailing edges of the pulses.//

- IN://All 32 dECL inputs are used to receive individual channel hits://The 2277 can be programmed to latch (the leading and/or the trailing edges of the pulses://

- TRIG PAIR OUT: All 16 dECL outputs provide signals to be used for external triggering Input pulses are pairwised OR'ed (0 & 1, 2 & 3, etc.) to create each output pulse. The 2277 can be programmed to provide triggering in either a latched mode or a pulsed mode. See section 4.3 for a complete description of latched versus pulsed modes.

#### 2.6 CAMAC Commands and Functions

In typical operation,/the crate controller issues a CAMAC command which includes specifying a station number (N), a subaddress (A), and a function code (F)//In response,/the module will generate a valid command accepted or a X response/If the command requires a response,/the module will act on the command and produce a Q response/For further information on CAMAC protocol/read "Introduction to CAMAC" found in the LeCroy Research Instrumentation Catalog//The commands recognized by the 2277 are listed and briefly described below//

• (F0-A0-S1) Read Data: The data can be read as soon as the module produces a Look-at-Me (LAM). This can occur as quickly as 5.12 µs after the COMMON STOP HIT) or (the COMMON START TIMEOUT). The 2277 needs no subaddressing for proper readout. If the data word read is valid, a Q equal to one will be generated. The end of valid data occurs when a word is read out with Q equal to zero and Buffering in Progress is false. See section 2.8 for data word bit

#### Product Description

definitions.//

- (F1-A0-S1) Read Status: This command allows the user to read status of the control register. Both an X and a Q response will be generated.

- (F8-A0-S1) Test LAM:/This command presents the state of the Look -at-me (LAM) on the Q bus line./An X response will always be generated and a Q response will be generated if a Look-at-me is present.//

- (F9-A0-S1) Clear: Command clears all channels of the module, but maintains the integrity of the control register. Either a front panel or a CAMAC clear must be issued to reenable the module for acquisition if the entire event has not been readout. The 2277 is ready to accept hits 60 nsec after the trailing edge of the clear arrives at the board. Both an X and a Q response will be generated.

- (F10·A0·S1) Clear LAM: Clears the LAM source in the module Both an X and a Q response will be generated.

- (F17-A0-S1) Program Status: Programs the control register which controls the operating mode of the module Both an X and a Q response will be generated. See section 2.7 for status bit definitions.

- (F24-A0-S1) Disable LAM:/Disables the LAM source./Both an X and a Q response will be generated.//

- (F25-A0-S1) Test Cycle: This command creates an internal tester cycle as determined by the control register. An F25-0-S1 should only be done when the board is in acquisition mode, meaning the 2277 has been cleared and is waiting for hits. Both an X and a Q response will be generated.

- (F26-A0-S1) Enable LAM: This command enables the Look-at-Me source. The module powers up with the LAM already enabled. Both an X and a Q response will be generated.

- (F27-A0-S1) Test BIP: This command allows the user to determine the status of the Buffering In Progress signal. While BIP is true, the data is being buffered and the data is not guaranteed to be ready. An X response will always be generated and a Q response will be generated if BIP is true.

- (F27-A1-S1) Test BUSY This command allows the user to determine the status of the BUSY signal While BUSY is true, the 2277 front end is disabled and will not latch hits //An X response will always be generated and a Q response will be generated if BUSY is true. //

- (C+Z·S2) Master Reset://A C or a Z clears all channels and resets the control register to zero// Both an X and a Q response will be generated.//

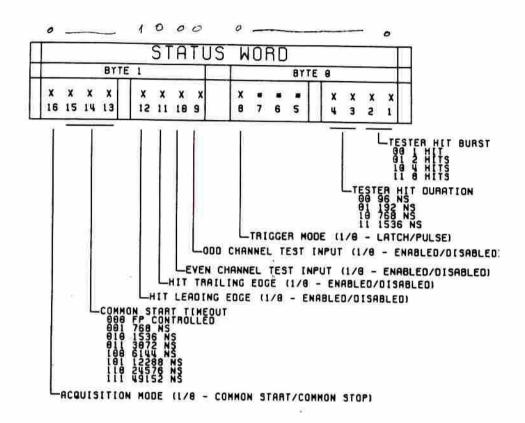

#### 2.7 Control Word

The Model 2277 has a 16 bit control register which controls the acquisition mode, the common start timeout, leading and trailing edge selection, even and odd channel test input selection, the trigger mode and the internal test patterns. The control register may be programmed using the CAMAC code, F17-A0-S1/The value of the control register can be read with the CAMAC code, F1-A0-S1/See table 2-1 below for individual bit definitions.

After a power-on, the state of the control register is undetermined. The CAMAC initialization function C or Z will set the control register to zero. The control register must be programmed before it will register hits. The CAMAC clear function (F9-A0-S1) has no effect on the control register.

The functions of the 16 control register bits are:/

- Acquisition Mode: Bit 16 determines whether the module will operate in common start or common stop mode. When a one is written the board operates in common start mode, and when a zero is written the board operates in a common stop mode. When read, the status of the bit is presented.

- Common Start Timeout:/Bits 13-15 determine the length of the common start timeout /The timeout can be provided via the front panel in which case bits 13-15 should be zeroes, or a timeout between 1,024 nsec and 65,536 nsec can be programmed /When read, the status of the bits is presented/

- Hit Leading Edge: Bit 12 determines whether the 2277 will latch the leading edges of the hits (received via the front panel connector marked IN, the front panel connector marked TEST or from the internal tester). When a one is written the leading edges of the hits are latched, and when a zero is written the leading edges of the hits are not latched. When read, the status of the bit is presented.

- Hit Trailing Edge: Bit 11 determines whether the 2277 will latch the trailing edges of the hits (received via the front panel connector marked IN, the front panel connector marked TEST or from the internal tester) // When a one is written the trailing edges of the hits are latched, and when a zero is written the trailing edges of the hits are not latched // When read, the status of the bit is presented //

- Even Channel Test Input: Bit 10 determines whether the even channels of the 2277 will latch the test inputs (received via the front panel connector marked TEST or the internal tester). When a one is written the even channels of the 2277 will latch test hits, and when a zero is written the even channels will not latch test hits. When read, the status of the bit is presented.

- Odd Channel Test Input. Bit 9 determines whether the odd channels of the 2277 will latch the test inputs (received via the front panel connector marked TEST or the internal tester). When a one is written the odd channels of the 2277 will latch test hits, and when a zero is written the odd channels will not latch test hits. When read, the status of the bit is presented.

- Trigger Mode: Bit 8 determines whether the 2277 will present a latched or a pulsed trigger output. When a one is written, the 2277 will latch the hit for a given channel and the corresponding signal coming out of the front panel connector marked TRIG PAIR OUT will remain true until the module is cleared. When a zero is written, the 2277 will provide a dECL pulse via the front panel connector marked TRIG PAIR OUT each time a given channel receives a hit. When read, the status of the bit is presented.

- Unused://Bits 5-7 are not used//However the bits are physically available,/thus they may be programmed to any status//When read, the status of the bits is presented.//

- Tester Hit Duration:/Bits 3 and 4 determine the width of the internal tester's hit pulses./The width can be programmed to be 128, 256, 1,024, or 2,048 nsec when a 0, 1, 2 or 3 are written respectively./When read, the status of the bits is presented.//

- Tester Hit Burst Bits 1 and 2 determine the number of pulses the internal tester will create. The internal tester can be programmed to create 1, 2, 4 or 8 pulses when a 0, 1, 2 or 3 are written respectively. When read, the status of the bits is presented.

Note the X's represent used bits and the \*'s represent unused bits.

TABLE 2-1 Status Word Definition

# 2.8 Output Word

The 2277 data is read out as a 22 bit data word/The 16 least significant bits are the data, the next bit is the hit phase (denoting leading or trailing edge), and the next 5 bits are the channel information // The hit phase is one for a leading edge hit) and (zero for a trailing edge hit)/The data can be read from the board using the CAMAC code, F0-A0-S1; no subaddressing is necessary.//

|    |    |    | BYT | E 2 |    |    |    |      |    |    |    | BYT | E 1 |   |   |   |   |   |   | 811 | E 8 |   |   | - |

|----|----|----|-----|-----|----|----|----|------|----|----|----|-----|-----|---|---|---|---|---|---|-----|-----|---|---|---|

|    |    | X  | x   | x   | X  | X  | x  | )    | (  | X  | X  | X   | x   | x | x | x | × | X | x | x   | ×   | x | x | x |

| 24 | 23 | 22 | 21  | 28  | 19 | 18 | 17 | - 12 | 16 | 15 | 14 | 13  |     |   |   |   | 8 | 7 | 6 | 5   | ų,  | 3 | 2 | 1 |

TABLE 2-2 Output Data Word Definition

# Installation

#### 3.1 General Installation

The LeCroy Model 2277 TDC is intended for use within a standard CAMAC crate such as the LeCroy Model 8025 CAMAC Crate with 25 slot positions or the Model 8013A with 13 positions. //The following voltage sources must be properly connected to the backplane: +6 V , -6 V and +24 V //Each crate must be controlled by either a slave or an intelligent controller //The controller must occupy the rightmost slot of the crate //Its purpose is to issue CAMAC COMMANDS to the modules and transfer information between a computer (or other digital device) and the CAMAC modules //LeCroy offers several such crate controllers, including the Model 8901A //The 8901A is a GPIB/CAMAC slave interface that operates as a "Talker/Listener", allowing the crate to act as one GPIB instrument //

With the power off, the 2277 is inserted into one of the slots of the CAMAC crate//The edge connector on the module should mate with the bus connector with modest pressure./The thumb screw located on the lower edge of the card should be engaged and tightened./Note the slot number of the module, as it will later be used for addressing.//

#### 3.2 Cables

The optimal method of cabling is the use of coax cables as signal cables. They generally result in less noise pick-up and less crosstalk. However, the use of twisted-pair cables generally results in lower cabling costs and typically higher density, thus the 2277 was designed to accept 34 connector ribbon cable. If using twisted-pairs, care should be taken to install high quality, shielded cables to minimize the effects of noise and crosstalk. Many of such cables can be purchased from LeCroy Corporation. In particular, there are two types of 34 conductor multiwire cables available, one for short connections using flat cable and the second for long connections using twisted and flat ribbon cable.

The model numbers of such cables are as follows://

- STC-DC/34/L flat multiwire cable for short interconnections

- LTC-DC/34-L or DC2/34-L twisted-pair multiwire cable for long interconnections

- STP-DC/02-L single twisted-pair cable, 3 ft maximum length

NOTE that L is the length in feet that must be specified by the user.

All inputs are differential ECL and terminated by 112 ohms./The terminations are SIP components and may be easily replaced to accommodate other characteristic impedances.

Installation

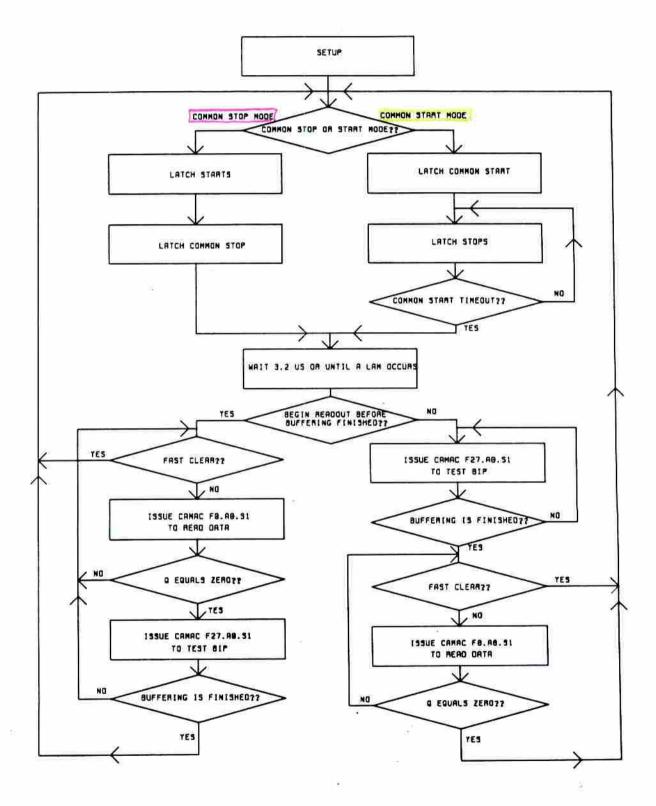

## 4.1 General Operation

The operation of the 2277 can be divided into four unique phases. The first phase includes all the setup necessary before the 2277 TDC can successfully be used. This includes installation of the module and programming the control register. The module will not latch hits until the control register has been programmed. Once all the setup is complete, the module is in acquisition mode and ready to accept hits. The module remains in acquisition mode until either a common stop) or (a common start) timeout occurs depending on the acquisition mode programmed. Following acquisition mode, the module buffers the data in a single event data buffer. It can take up to 5.12 usec for the first dataword to be buffered. The first dataword has been buffered once the module issues a Look-at-me demanding attention. While the data is being buffered, the Buffering-In-Progress (BIP) signal is true. The user can begin the final phase, readout, either after or while the buffering is in progress. If the user begins the readout phase while the data is being buffered, it is possible for the user to issue a CAMAC read and receive an invalid word. The invalid word is easily identified because its Q will be false. If the user waits until after the buffering has been finished, an invalid data word indicates end of event. Refer to the flowchart provided in figure 4-1 for further assistance.

Figure 4-1 2277 General Operation Flowchart

## 4.2 Common Start vs. Common Stop Modes

The LeCroy Model 2277 TDC was designed to operate in both Common Start) and Common Stop modes. Sensitivity for the individual channel input pulses can be programmed in the control register to trigger on either (the leading) and/or the trailing edge. In either mode, channels can store the time interval of a maximum of 16 edges. The common hit (stop or start), always measures from the leading (low-to-high transition) edge.

When in Common Stop Mode, the individual hit pulses must precede the common stop pulse. The hit pulses are received via the front panel inputs marked IN, and the common pulse is received via either of the front panel inputs marked COM. Time is measured from the leading and/or trailing edges of the hits to the leading edge of the common stop pulse. In Common Stop Mode, the last 16 edges before the common are recorded with earlier hits being discarded. The module 2277 will not accept multiple common input pulses.

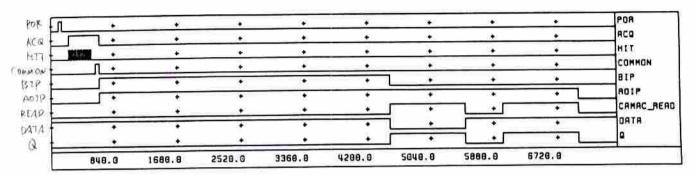

Figure 4-2 demonstrates proper timing of the signals in Common Stop mode where 16 start pulses have been provided via the hit input and a stop pulse has been provided via the common input. After a power-on which creates a Power on Reset pulse to the module (POR), the 2277 is in acquisition mode and is ready to accept hits provided the control register has been programmed properly. If both edges of the 2277 were enabled, all 16 edges shown in the figure would be latched. The leading edge of the COM stop pulse disables the 2277 from accepting further HITs. The common pulse must be at least 20 nsec wide and the trailing edge must arrive before readout can occur. The 2277 can be readout via CAMAC as quickly as 5.12 usec after the leading edge of the common stop pulse provided the trailing edge of the common stop pulse has arrived. If the module's Look-at-me (LAM) has been enabled, readout can begin as soon as a LAM occurs. However, valid data cannot be guaranteed until Buffering in Progress (BIP) becomes false which could take up to 240 usec. See section 4.6 for more information regarding the BIP signal. The front end is prohibited from accepting inputs while the BUSY signal is true. The BUSY signal is true until either the TDC detects a CLR pulse or (all the current event's data has been readout). The module will accept either CAMAC or a front panel clear) at any time. The front panel CLR signal must be at least 20 nsec wide. The module will automatically return to acquisition mode 60 nsec after the trailing edge of the clear pulse.

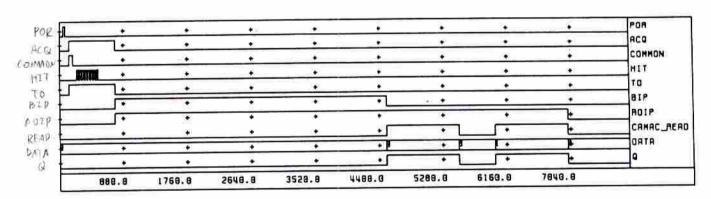

When operating in Common Start Mode, a full scale time hit window is necessary. The hit window determines the period during which the module will latch hits. The hit window begins when the module detects a start via the COM input and ends when the module receives a timeout pulse. The common start timeout is CAMAC programmable, or it may be provided via the front panel input marked T-IN. If a timeout, either from the front panel or (internally generated as programmed), is not provided within 65,536 nsec after the leading edge of the start pulse, the module uses a default timeout and disables itself. The window is opened immediately following the leading edge of a COM input pulse or a start, and it is closed after 65,536 nsec. While the window is open, the module will latch the leading and/or (trailing) edges of all pulses received either via the front panel connectors marked IN, the front panel connector marked TEST or the internal tester. Hits received after the timeout window has closed are not recorded. In the event more than 16 hits arrive during the hit window, those 16 hits furthest in time from the common start are registered. Multiple common hits are not accepted.

Figure 4-3 demonstrates proper timing of the signals in Common Start mode where a start pulse has been provided via the COM input and 16 stop pulses have been provided via the input labeled IN //As in Common Stop mode, the 2277 enters acquisition mode immediately after a power-on (POR) // Provided the Hit Leading Edge and the Hit Trailing Edge bits have been enabled, the 2277 will latch all edges received after the leading edge of the common start input pulse // There must be at least 20 nsec between selected edges in order for the hits to be latched // The common start input pulse must be at least 20 nsec wide and the trailing edge must arrive before readout can occur // Readout can occur as quickly as 5.12 µsec after the trailing edge of the common start timeout has arrived, or if the module's Look-at-me (LAM) has been enabled, readout can begin as soon as a LAM occurs // To read the entire event,/continue to issue read data commands until Q becomes false // If the Buffering In Progress (BIP) signal is also false, the event has been completely readout // However if the BIP signal is true, the data is still being buffered // The front end is prohibited from accepting inputs while the BUSY signal is true. // The BUSY signal is true until either the TDC detects a CLR pulse or all the current event's data has been readout // All data which is returned with Q equal to zero is not valid //

SIZa Vice

Note that the scale at the bottom of the figures are in nsec.

Figure 4-2 An example of proper signal timing for operation in Common Stop Mode.

Figure 4-3 An example of proper signal timing for operation in Common Start Mode.

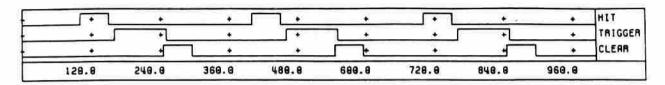

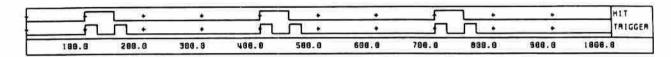

#### 4.3 Pulse vs. Latch Modes

Sixteen dECL front panel trigger outputs marked TRIG PAIR OUT are available to the user for external trigger logic//Neighboring channels are "pairwised OR'ed" (0 & 1, 2 & 3, etc.) to produce a true trigger out when either of the channels receives a hit.//The trigger outputs can be programmed to work in either/a Pulsed or/a Latched) Mode by programming bit 8 of the control register // See Section 2.7 for further information on programming the control register // When in Latched Mode, the trigger outputs are cleared by either a front panel clear, a CAMAC clear or when events are read out of the MTD132//When in Pulse Mode the trigger outputs remain logic true for approximately 20 nsecs, and then they are cleared//

the clear signal /The clear signal must have a width of at least 20 nsec /If a clear signal arrives during readout, the remainder of the current event's data will be corrupted //

- IN://The two 34 pin connectors on the front panel marked IN are used to receive the pulses whose times are to be measured from the COM input pulse./In Common Stop Mode,/the pulses mark the beginning of the time interval which is digitized by the 2277/In Common Start Mode, the pulses mark the end of the time interval which is to be digitized.//

- COM:/The two front panel inputs marked COM are used to accept the common input pulse./In Common Start Mode, the leading edge marks the beginning of the time interval which is digitized by the 2277./In Common Stop Mode, the leading edge marks the end of the time interval which is digitized//Two front panel inputs are available for daisy chaining several modules together./See Section 4.7 for further details on daisy chaining the 2277.//

- T-IN:/When operating in Common Start Mode,/it is necessary to supply a full scale window/

The window is a defined period during which the module will latch hits//The window begins

after a start pulse and ends when the module receives a timeout pulse//This timeout pulse may

be provided on board by programming the control register appropriately as explained in Section

2.7//Alternately, an external timeout may be provided via the front panel input marked T-IN//

If the trailing edge of the front panel hit window does not occur within 65,535 nsec after the

leading edge of the common input pulse (start),/the module uses a default timeout and disables

the board from accepting further hits//When using the front panel timeout,/bits 13-15 of the

control register should be set to 0.//

- TEST:/For testing purposes, a front panel input marked TEST is available./In Common Stop Mode, pulses received via the test input marked TEST begin the time interval to be digitized and the common input marked COM provides the stop://In Common Start Mode,/the common input provides the common start,/and the test input provides the stops://The last 16 enabled edges provided via the test input are stored.//For example,/if both (the Hit Leading Edge) and (the Hit Trailing Edge) bits of the control register are enabled,/the last 16 edges will be stored.// However, if only the Hit Leading Edge bit is enabled,/the last 16 leading edges will be stored.//

# 4.5 Front Panel Outputs

All Front panel outputs are differential ECL and are asserted when the pin labeled "+" is ECL high and the pin labeled "-" is ECL low//All outputs are described below://

- BUSY:/BUSY is a single dECL signal provided to aid in readout//BUSY is true to indicate when

the 2277 inputs are inhibited//At power-up, BUSY is false and the module is ready to accept

inputs./When the module receives either a common start timeout or a common hit,/depending

on the mode/ BUSY becomes true and the module will no longer respond to IN inputs//BUSY

remains true until the module is cleared,/a master reset is issued or the user has completely read

out the module//

- TRIG PAIR OUT: Sixteen dECL outputs are provided for external triggering purposes. Input pulses received via the front panel inputs, the front panel TEST input or the internal tester are pairwised OR'ed (0 & 1, 2 & 3, etc.) to create each trigger output. When in latched mode, the output is set by an input pulse and is not reset until the 2277 receives a clear or is readout. When in pulsed mode, the output creates a pulse for each latched input edge. See section 4.3 for a complete description of latched versus pulsed modes.

# 4.6 Reading the Data

The user may read out the 2277 as quickly as 5.12 usec after the module receives either a common start timeout) or a common stop hit, depending on the mode. When the module receives either a common start timeout or a common stop hit, the BUSY signal becomes true and the module will no longer respond to inputs. The 2277 immediately begins to transfer valid data to the single event buffer. While the 2277 is transferring the data, the Buffering In Progress (BIP) signal is true. The BIP signal can be tested by issuing a CAMAC F27-A0-S1 Test BIP command. If the module is still buffering the

Figure 4-4 Example of timing relationship between hits and the trigger outputs when operating in Latch Mode.

Figure 4-5 Example of timing relationship between hits and the trigger outputs when operating in Pulse Mode.

### 4.4 Front Panel Control Signal Inputs

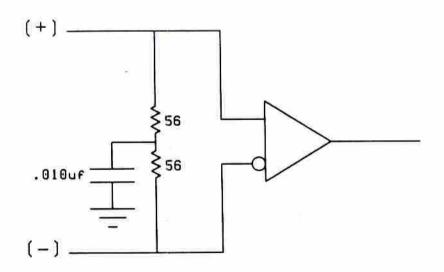

All Front panel control signals are differential ECL and are asserted when the pin labeled "+" is ECL high and the pin labeled "-" is ECL low ||All inputs are terminated by 112 ohms, as shown ||The terminations are SIP components and may be easily replaced to accommodate other characteristic impedances.||

Figure 4-6 ECL Terminations

All front panel inputs are dECL and are briefly described below://

CLR#A clear signal may be sent to the module at any time via the front panel input marked CLR.#All channels of the module are immediately cleared without changing the status of the control register. The module enters acquisition mode and is ready to accept hits 60 nsec after data, Q will return a true response. After BIP becomes false, it is safe to readout the data by issuing a F0-A0-S1 read data command. To read the entire event, continue to issue read data commands until Q is false indicating the end of event. The last data word returned with Q equal to zero is not valid.

However, the data can be read out before the buffering has finished provided the user waits 3.2 µsec after the end of acquisition or a Look-at-Me occurs./If reading before the end of the buffering./it is possible the user will read a Q equal to zero which does not indicate the end of event./ but rather that the next data word was not ready./To determine the meaning of the false Q,/it is necessary to issue a CAMAC F27-A0-S1 Test BIP command.//If BIP is returned true, the module is still buffering data.//If BIP is returned false, the false Q is indicative of the end of event.//

The module will automatically be returned to acquisition mode/if the user reads out all data//

However, in the event the user wishes to return to acquisition mode before the entire event has been read, either a CAMAC/or a front panel clear/can be issued.//The clear signal clears the single event buffer and returns the module to acquisition mode 60 nsec after the end of the clear pulse/

### 4.7 Daisy Chaining the 2277

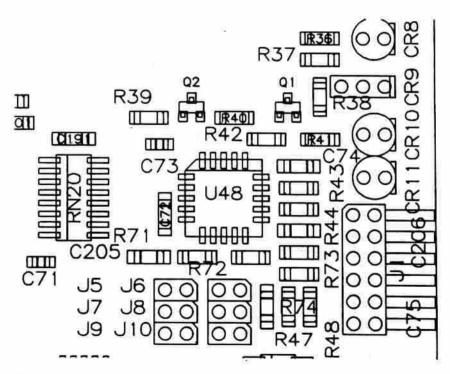

Two COM connections are implemented on the 2277 TDC for easy board to board distribution of the common input pulse./Daisy chaining may be achieved by simply connecting the COM input of one module to the COM input of another module./The termination network for each board should only be left on the last board in the chain, thus the jumpers J5 and J6 should be removed from every module except for the last one in the chain when daisy chaining./The termination networks for the TIME IN signal and the FP CLEAR signal are also jumpered to ease in daisy chaining modules./See figure 4-7 for assistance in identifying jumpers J5 and J6 of the COM termination network, jumpers J7 and J8 of the TIME IN termination network, and jumpers J9 and J10 of the FP CLEAR termination network.//

Figure 4-7 Front Panel COM Input Termination Network

#### 4.8 Internal Tester

An internal tester has been implemented on-board the module 2277 TDC for testing and calibration purposes. The internal tester can be programmed to produce 1, 2, 4, or 8 pulses with a pulse width of 128, 256, 1,024, or 2,048 nsecs. Leading and/or trailing edge selection is permissible allowing the internal tester to produce up to sixteen edges. The internal tester can operate in either Common Start or Common Stop Mode.

A test cycle is initiated by issuing the CAMAC command F25-A0-S1.//A test cycle should only be performed when the module is in acquisition mode,/meaning 60 nsec after the trailing edge of a clear pulse.//The default status for the internal tester will produce a single hit pulse with a width of 128 nsec.// Provided the Hit Leading Edge and the Hit Trailing Edge bits of the control register are enabled, the single event buffer will store 64 data words with each channel's data similar to that shown below:

| Raw Data | Hit Phase | Channel Number | Time Measurement (in bins) |

|----------|-----------|----------------|----------------------------|

| 0x10c02  | 1         | 0              | 3074                       |

| 0x00b84  | 0         | 0              | 2948                       |

It should be noted, the internal tester is not particularly useful for calibrating the 2277/The front panel TEST input would be of much greater use for calibration purposes/However, it is quite useful for testing the single event buffer, the control register and the overall functionality of each channel/

## 4.9 Testing the 2277 using the Internal Tester

- 1. Install the module in the crate as indicated in the Installation section.

- 2. Power up the crate.

- 3. Issue a Master Reset to the module using a CAMAC C or Z.

- 4. Write 0F0F (hex) to the control register of the 2277 via CAMAC using a F17-A0-S1. This will place the module in Common Stop Mode, enable both the odd and the even channels for testing, enable both the leading and the trailing edges, and put the trigger in Pulse Mode. The internal tester will be set to produce 8 pulses with a width of 2,048 nsec.

- 5. Read the control register to be certain all the bits are functioning using a F1-A0-S1.

- 6. Create a test cycle by writing a F25-A0-S1.

- 7. Wait 5.12 µs or until a Look-at-Me occurs, then test the Buffering in Progress signal by issuing a CAMAC F27-A0-S1. If Q is true, reissue the command until buffering is complete.

- 8. Read the data using a F0-A0-S1. Continue to read the data until Q is false. Q equal to zero signifies all data has been readout and the current data word accompanying Q equal to zero is invalid.

- 9. To test the module in common start mode, write ff00 (hex) to the control register, and repeat steps 5 through 7. Other test patterns can be created as well.

# 4.10 Testing the 2277 Using the Test Input

- 1. Install the module in the crate as indicated in the Installation section.

- 2. Power up the crate.

- 3. Issue a Master Reset to the module using a CAMAC C or Z.

- 4. Write 0F00 (hex) to the control register of the 2277 via CAMAC using a F17-A0-S1. This will place the module in Common Stop Mode, enable both the odd and the even channels for testing,

enable both the leading and the trailing edges, and put the trigger in Pulse Mode.

- 5. Read the control register to be certain all the bits are functioning using a F1-A0-S1.

- 6. Provide an external common stop pulse by connecting a twisted-pair cable from an external pulser to the front panel input marked COM. Provide external hits by connecting twisted-pair cables from an external pulser to the test input marked TEST. Make certain the start pulses reach the test inputs before the stop pulse reaches the common input.

- 7. Wait 5.12 µs or until a Look-at-Me occurs, then test the Buffering in Progress signal by issuing a CAMAC F27-A0-S1. If Q is true, reissue the command until buffering is complete.

- 8. Read the data using a F0·A0·S1. Continue to read the data until Q is false. Q equal to zero signifies all data has been readout and the current data word accompanying Q equal to zero is invalid.

- 9. Write FF0F (hex) to the control register to test the module in Common Start Mode. Exchange the test input cable with the common input cable. Repeat steps 5 though 7.

## 4.11 Example Code

Included below is an example of code written in C to use as a reference when operating the 2277. The example code assumes the user has linked to a library containing IEEE standard subroutines for CAMAC. For a further explanation of such subroutines, refer to the IEEE Standard Subroutines for CAMAC (ANSI/IEEE Std 758-1979) published by The Institute of Electrical and Electronics Engineers.

The example assumes a crate full of 2277's. Only the LAM of the first 2277 has been enabled. It is assumed that this 2277 will always receive a trigger. Once the lead 2277 has issued a Look-at-me, the remainder of the 2277's will be readout. After the data has been readout, the data is written to file.

```

example.c - An example of typical 2277 operation using IEEE Standard Subroutines for CAMAC.

#include <stdio.h>

#include <graph.h>

#include <math.h>

#include <conio.h>

/* prototypes */

extern int cfsa( int function_code, int ext_add, long *camac_data_word, int *q );

extern int cccc( int ext_add );

extern int cdreg( int *ext_add, int branch_number, int crate_number, int station_number, int

subaddress);

extern int main( void );

/* branch number */

#define BRANCH 0

/* crate number */

#define CRATE 0

/* station numbers */

#define FIRST_SLOT 1

#define LAST_SLOT 23

```

```

/* subaddress - The 2277 has no subaddress except zero! */

#define ADDRESS 0

main()

/* CAMAC x and q responses */

int x = 0, q = 0;

/* program parameters */

int ext_address[LAST_SLOT - FIRST_SLOT + 1];

int i, slot2277, ext;

unsigned int event_num = 0;

FILE *stream;

long data_word;

long status = 0x0f00;

long zero = 0x0;

/* Calculate the address for each 2277 module to be addressed. The calculated addresses will be stored

in the array ext_address[]. */

for( slot2277 = FIRST_SLOT; slot2277 <= LAST_SLOT; slot2277++ )

cdreg( &ext, BRANCH, CRATE, slot2277, ADDRESS );

ext_address[slot2277 - FIRST_SLOT] = ext;

/* Reset the 2277's in the crate defined by the variable ext_address∏ by causing a Dataway Clear (C). */

cccc( ext_address[0] );

/* Enable the Look-at-me for the first 2277. Assume the first 2277 will receive a trigger if the other

2277's receive triggers.*/

cfsa(26, ext_address[0], &zero, &q);

if( !q )

printf( "The LAM for the 2277 in slot %2d has not been enabled.\n", FIRST_SLOT);

/* Disable the Look-at-me for the other 2277's. */

for(i = 1; i < (FIRST_SLOT - LAST_SLOT + 1); i++)

cfsa(24, ext_address[i], &zero, &q);

printf("The LAM for the 2277 in slot %2d has not been disabled.\n", (i + FIRST_SLOT));

/* Program the control registers for each module. The control word STATUS is written to each 2277.

for(i = 0; i < (FIRST_SLOT - LAST_SLOT + 1); i++)

cfsa( 17, ext_address[i], &status, &q );

if( !q )

printf( "The status register for the 2277 in slot %2d is not properly programmed.\n", (i +

FIRST_SLOT) );

}

/* Open a file that the data readout from the 2277's can be stored. */

stream = fopen( "example.dat", "w" );

while(!kbhit())

/* Clear the 2277's to begin acquisition. */

for(i = 0; i < (FIRST_SLOT - LAST_SLOT + 1); i++)

cfsa( 9, ext_address[i], &zero, &q );

if( !q )

```

```

printf( "The 2277 in slot %2d has not been properly cleared.\n", (i + FIRST_SLOT) );

/* Do a test cycle. */

for (i = 0; i < (FIRST_SLOT - LAST_SLOT + 1); i++)

cfsa( 25, ext_address[i], &zero, &q );

if( !q )

printf( "Test cycle wasn't done in slot %2d.\n", i + FIRST_SLOT );

/* Wait for a LAM from the first 2277. Q represents the state of the LAM. */

cfsa(8, ext_address[0], &zero, &q);

while( !q && !kbhit() )

cfsa( 8, ext_address[0], &zero, &q );

/* Clear the Look-at-me of the 2277 in the lead slot. */

cfsa( 10, ext_address[0], &zero, &q );

/* Read out the 2277's until q equals zero and write the data to file. */

for( i = 0; i < (FIRST_SLOT - LAST_SLOT + 1); i++)

fprintf( stream, "event number: %u\t slot number: %2d\n", event_num, (i + FIRST_SLOT) );

while(bip)

cfsa( 0, ext_address[i], &data_word, &q );

while(q)

fprintf( stream, "%#6x\n", data_word );

cfsa( 0, ext_address[i], &data_word, &q );

if( !q )

cfsa( 27, ext_address[i], &zero, &q );

bip = q;

}

event_num++;

/* Close the data file */

fclose( stream );

return(0);

```

## Theory of Operation

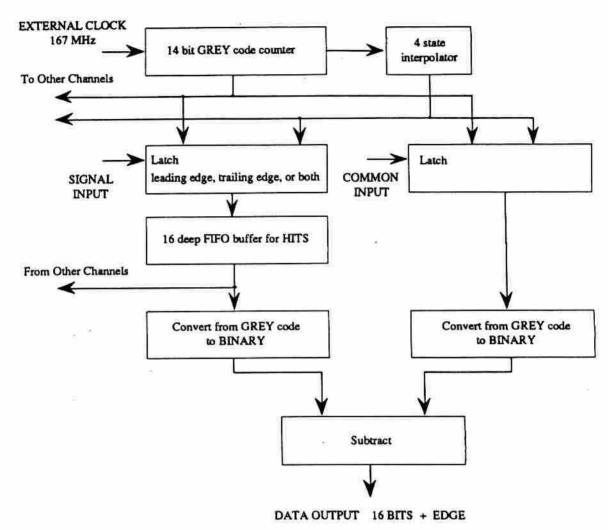

At the heart of the LeCroy Model 2277 TDC is the MTD132. The MTD132 is an eight channel Time to Digital Converter (TDC) implemented as a full custom CMOS ASIC. It combines a synchronous counter and an asynchronous interpolation system with eight parallel memory channels. Each channel is capable of recording the arrival of sixteen pulse edges with sixteen bits of dynamic range. Both Common Start and Common Stop operation are permitted with equal facility. On-chip sparse data readout is implemented, with all possible ambiguities resolved.

## 5.1 Gray Code Counter Coarse Time Measurement

A sixteen bit gray code counter provides the backbone of the time measurement system. This counter is executed using a bitwise-pipelined and interleaved divide by two technique. Two-way interleaving permits the count frequency to be double that of the counter clock frequency. The counter output is buffered and distributed to the eight channel memories and to the common register.