## Operator's Manual

MEMORY MODULE MODEL 8800A

**LeCroy**

Innovators in Instrumentation

#### GENERAL INFORMATION

**PURPOSE**

This manual is intended to provide instruction regarding the setup and operation of the covered instruments. In addition, it describes the theory of operation and presents other information regarding its functioning and application.

The Service Documentation should be consulted for the schematics, parts lists and other materials that apply to the specific version of the instrument as identified by its ECO number.

UNPACKING AND INSPECTION

It is recommended that the shipment be thoroughly inspected immediately upon delivery. All material in the container should be checked against the enclosed Packing List and shortages reported promptly. If the shipment is damaged in any way, please notify the Customer Service Department or the local field service office. If the damage is due to mishandling during shipment, you may be requested to assist in contacting the carrier in filing a damage claim.

VARRANTY

LeCroy warrants its instrument products to operate within specifications under normal use and service for a period of one year from the date of shipment. Component products, replacement parts, and repairs are warranted for 90 days. Software is thoroughly tested, but is supplied "as is" with no warranty of any kind covering detailed performance. Accessory products not manufactured by LeCroy are covered by the original equipment manufacturers warranty only.

In exercising this warranty, LeCroy will repair or, at its option, replace any product returned to the Customer Service Department or an authorized service facility within the warranty period, provided that the warrantor's examination discloses that the product is defective due to workmanship or materials and has not been caused by misuse, neglect, accident or abnormal conditions or operations.

The purchaser is responsible for the transportation and insurance charges arising from the return of products to the servicing facility. LeCroy will return all in-warranty products with transportation prepaid.

This warranty is in lieu of all other warranties, express or implied, including but not limited to any implied warranty of merchantability, fitness, or adequacy for any particular purpose or use. LeCroy shall not be liable for any special, incidental, or consequential damages, whether in contract, or otherwise.

PRODUCT ASSISTANCE Answers to questions concerning installation, calibration, and use of LeCroy equipment are available from the Customer Services Department, 700 Chestnut Ridge Road, Chestnut Ridge, New York 10977-6499 (914) 578-6059, or your local field service office.

#### MAINTENANCE AGREEMENTS

LeCroy offers a selection of customer support service. For example, Blue Ribbon service provides guaranteed three-day turn around on repairs, a direct access number for product application assistance, yearly calibration and the addition of engineering improvements. Maintenance agreements provide extended warranty that allows the customer to budget maintenance costs after the initial warranty has expired. Other services such as installation, training, on-site repair, and addition of engineering improvements are available through specific Supplemental Support Agreements. Please contact the Customer Service Department or the local field service office for details.

#### DOCUMENTATION DISCREPANCIES

LeCroy is committed to providing state-of-the-art instrumentation and is continually refining and improving the performance of its products. While physical modifications can be implemented quite rapidly, the corrected documentation frequently requires more time to produce. Consequently, this manual may not agree in every detail with the accompanying product and the schematics in the Service Documentation. There may be small discrepancies in the values of components for the purposes of pulse shape, timing, offset, etc., and, occasionally, minor logic changes. Where any such inconsistencies exist, please be assured that the unit is correct and incorporates the most up-to-date circuitry.

-

## SOPTWARE LICENSING AGREEMENT

Software products are licensed for a single machine. Under this license you may:

- · Copy the software for backup or modification purposes in support of your use of the software on a single machine.

- Modify the software and/or merge it into another program for your use on a single machine.

- Transfer the software and the license to another party if the other party accepts the terms of this agreement and you relinquish all copies, whether in printed or machine readable form, including all modified or merged versions.

#### ATTENTION

3

3

=

3

3

=

3

=

=

=

à

i

SEE POCKET IN BACK OF MANUAL FOR SCHEMATICS, PARTS LISTS, AND ADDITIONAL ADDENDA WITH ANY CHANGES TO MANUAL.

CRATE POWER SHOULD BE TURNED OFF DURING INSERTION AND REMOVAL OF UNIT TO AVOID DAMAGE CAUSED BY MOMEMTARY MISALIGNMENT OF CONTACTS.

ATTENTION

### TABLE OF CONTENTS

Page Number

3

-

- 3

-

- 7

- 3

-

-3

3

- 3

-

-3

-

- 1

| SECTION | 1 -  | SPECIFICATIONS                 |     |

|---------|------|--------------------------------|-----|

|         | Tech | nnical Data Sheet              |     |

| SECTION | 2 -  | OPERATING INSTRUCTIONS         |     |

|         | 2.1  | General                        | 2-1 |

|         | 2.2  | Front Panel Indicator          | 2-1 |

|         | 2.3  | Rear Edge-Connector Signals    | 2-1 |

|         | 2.4  | Switch Settings                | 2-2 |

|         | 2.5  | Power                          | 2-4 |

| SECTION | 3 -  | FUNCTIONAL CIRCUIT DESCRIPTION |     |

|         | 3.1  | General                        | 3-1 |

|         | 3.2  | Writing Data                   | 3-1 |

|         | 2 2  | Reading Data                   | 3-1 |

# Model 8800A Memory Module

The Model 8800A is designed to provide data storage for a wide variety of LeCroy instruments, including transient recorders, video digitizers, and fast data loggers. Each module has a capacity for 32K 12-bit data words and modules may be cascaded to provide record lengths to 256K words.

All read and write operations to the 8800A are controlled by the companion digitizer. Data from the digitizer is sequentially stored as acquired; if the controlling unit has more than one channel, the total of all cascaded memory is divided equally among the active channels. During readout to the CAMAC dataway, the memory contents are reconstructed so that each channel's data is in contiguous time sequence.

Readout is nondestructive and the memory is protected against write operations from the CAMAC dataway; it can only be written from the companion digitizer.

The Model 8800A Memory module is compatible with the following LeCroy digitizers:

Model 22648 channel, 0.5 MHz 8-bit Waveform DigitizerModel 82104 channel, 1 MHz 10-bit Waveform DigitizerModel 8212A32 channel, 0.5-40 kHz, 12-bit Data LoggerModel 8212A/88 channel, 12.5-100 kHz, 12-bit Data Logger

Copyright@August, 1986 LeCroy Corporation

## SPECIFICATIONS CAMAC Model 8800A MEMORY MODULE

Inputs:

TTL Levels. Lines: 12 data, 12 grounds; 7 control lines, 7 grounds. One 40-conductor edge connector located at the upper rear of the module. Mates with LeCroy Model DC8800/n Data Cable (where "n" equals the number of memory modules linked to one data acquisition device.

Memory Active Light:

Front-panel LED indicates when memory is being loaded or read.

Memory Size:

32,768 words, 12 bits.

Memory Expansion:

Serial organization permits adding the Model 8800A modules in a daisy-chained fashion with the maximum memory size dictated by the control board of the ADC module. Memory size must be internally specified on the control board of the "front end" ADC (jumper option) and on the memory modules (onboard Programming Switch). The LeCroy Models 2264 and 8210 can drive three modules, and Model 8212A can drive four modules with larger memory extention possible as a factory option.

Packaging:

In conformance with the international CAMAC standard for nuclear modules (European ESONE Report #EUR4100 or U.S. IEEE Report #583). RF-shielded CAMAC #1 module.

Power Supplies:

The Model 8800A Series can draw + 12 V from the + 12 V CAMAC bus or can be jumpered internally to use a built-in + 24 to + 12 V converter. Since the memory is not read directly, it can be located in an adjacent power crate (<4 feet of cable) with only + 12, + 6 V power.

Power Consumption:

Voltage

Current

Power

+ 12 V (or + 24 V)

490 mA

5.9 W (11.8 W)

+ 6 V

650 mA

3.9 W

- 6 V

30 mA

0.2 W

Total Power Dissipated:

10 W (+ 12 V), 15.9 W (+ 24 V)

SPECIFICATIONS SUBJECT TO CHANGE

#### SECTION 2

#### 2. OPERATING INSTRUCTIONS

#### 2.1 General

-5

- 0

-01

-5

D

3

3

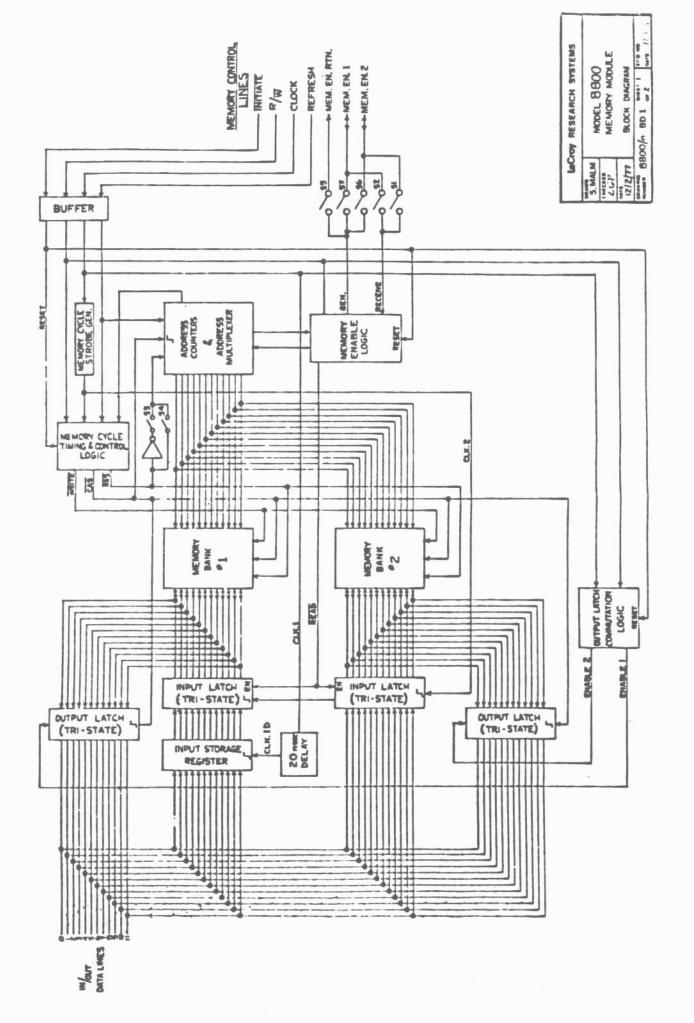

The LeCroy 8800A module is a dynamic memory with a capacity of 32,768 12-bit words. It is designed especially for high speed (up to 5 megawords/sec) sequential storage of data. The input data is multiplexed into two banks of 16K dynamic RAM memory and is then written into the memories in a page mode memory cycle as the memories are addressed by on board counters. During readout the data is multiplexed onto the I/O lines from the two memory banks in the same order that it was written into the memory. The entire memory (per digitizer channel) must be read out to reach the last word written.

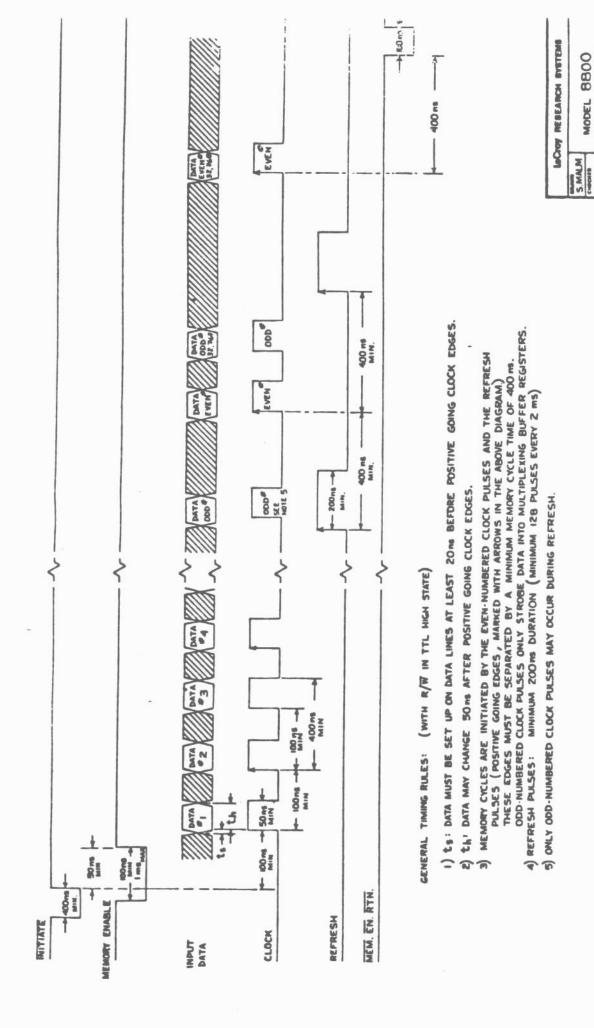

Since these units are dynamic RAM's the 128 rows in the memory banks must all be addressed at least once every 2 msec. When memory cycles occur at a rate too low to satisfy this condition, refresh cycles must be inserted by appropriately timed refresh pulses on the Model 8800A refresh control line. Multiplexing of the data into the memory and memory address increment are controlled by memory clock pulses on the memory strobe line. Read or write operation is determined by the logic level on the read/write control line. The logic circuits are reset or initialized by a TTL low pulse on the initialize line. In addition, these units are designed so that they may be cascaded to increase memory size. To facilitate this mode of operation, each module has two memory enable lines and a memory enable return line. All of the above mentioned control lines as well as the I/O lines for the data are accessed via a rear panel 40 pin header.

#### 2.2 Front Panel Indicator

An LED lamp lights when memory module is enabled for read or write operations. When cascaded memory modules are being used, this allows the user to see which module is currently receiving or dispensing data.

2.3 Rear Edge-Connector Signals (see Pin Assignments diagram, Figure 2.1)

INITIATE:

Minimum 400 nsec pulse to initialize memory address registers to zero and reset internal logic.

MEM1:

TTL low, indicates the module has been completely written or read. This signal is used to enable the next even 8800A to read or write data. Maximum signal duration should be between 100 and 150 nsec.

MEM 2:

Same as MEM1, except used to enable the next odd

8800A to read or write data.

MEM RTN:

Same as MEM EN lines except this signal is transmitted back to the digitizer module's controller. MEM EN RTN is generated by the last

memory module on the bus.

REFRESH:

TTL high pulse, minimum duration is 200 nsec. This signal initiates a refresh cycle in the memory module.

CLOCK:

TTL high pulse, minimum duration is 50 nsec. This signal stores data in the input latches during write operations. Alternate clock pulses initiate memory cycles. During readout the signal alternately enables bank #1 and #2 output latches (see functional description, Section 3) and alternate clock

pulses will initiate memory cycles.

R/W:

TTL high to write, low to read. Transition from high to low initiates memory cycle which locks data into output latches.

DATA LINES (211-20):

Bidirectional TTL data,  $2^{11}$  is the MSB and  $2^{0}$  is the LSB.

-

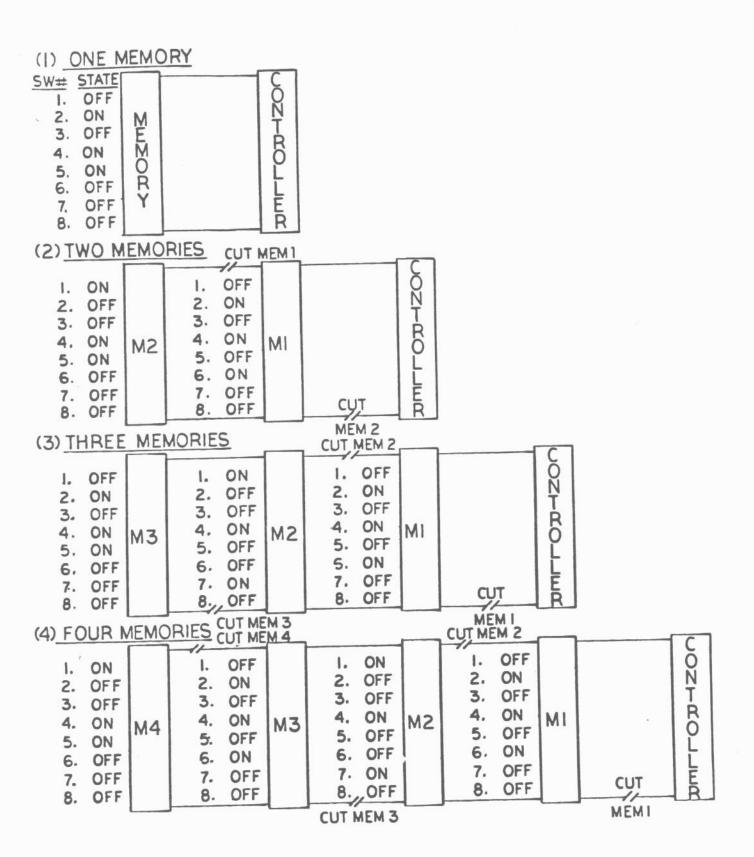

2.4 Switch Settings (Refer to memory cabling and switch diagram, Figure 2.2)

Seven switches in a DIP package are accessible through a window in the side cover of the 8800A. Five of the switches are used to program the module for a position in a chain of modules, i.e., the switch positions will determine whether the module is to function in a first, last or intermediate position in the chain. The remaining two switches program the scanning of the memory addresses to be either by row or by column.

General Rules - A memory module may receive or generate memory enable pulses on either MEM1 or MEM2, but may not receive and generate on the same line; thus switches S1 and S6 or S2 and S7 should never be on simultaneously. The memory may either be scanned by row or column\* thus switches 3 and 4 should always be in opposite states. A memory system may consist of a series of memory modules. The last module in the series must send a memory enable return (MEM RTN) pulse to the controller signalling the end of a memory scan or the beginning of a new memory scan, therefore switch 5 must be on only in the last module in the series.

-

-

-5

B

i

-3

-

B

B

-

3

1

B

-

3

-

=

11

1

Specific Example - The following example system will illustrate the use of the memory enable lines and detailed switch settings. If a chain of four memory modules are to be used to scan by row (i.e., each column element in a row is addressed before advancing to the next row), set switch 4 on and switch 3 off on all of the units.

Module #1 receives the enable pulse from the controller on MEM1, therefore, S2 must be on and S7 off. Module #1 must then send an enable pulse to Module #2 on MEM2, thus, S6 must be on and S1 off. To isolate the pulse on the MEM2 line from the controller, the MEM2 line between Module #1 and the controller must be cut.

Module #2 receives the enable pulse on MEM2, therefore S1 must be on and S6 off. Module #2 must now send an enable pulse to Module #3 on MEM1, thus S7 must be on and S2 off. To isolate this pulse on MEM1 from Module #1's MEM1 input, the MEM1 line between Module #1 and Module #2 must be cut.

Module #3 receives the enable pulse on MEM1, therefore S2 must be on and S7 off. The enable pulse to Module #4 must be sent on MEM2, thus S6 must be on and S1 off. To isolate this pulse from Module #2, the MEM2 line between Module #3 and Module #2 must be cut.

Module #4 receives the enable pulse MEM2, therefore S1 must be on and S6 off. Since Module #4 is the last in the chain it must send a memory enable return pulse back to the controller, thus S5 must be on (S5 on the first three modules must be off). S2 and S7 could both be turned off to disconnect MEM1 between Module #3 and Module #4, but it is recommended that MEM1 be cut between these modules.

The MEM1 and MEM2 lines are the outside (upper and lower) control lines facilitating the necessary alternating cuts in these lines between units on the system.

\* Scanning by column also requires an internal jumper connection (AG, pin 10).

#### 2.5 Power

Since the 16K dynamic RAM's use +12 volts, an internal voltage regulator is supplied which will drop +24 volts to +12 volts. However, for CAMAC crates which supply power to their +12 V bus lines, the 8800A has internal jumpers (see schematic) allowing operation from +12 V which is in fact recommended due to lower total power dissipation.

The 8800A memory module uses no CAMAC control or data lines and may be placed in a dummy crate which contains power only. Consult factory concerning maximum bus cable lengths.

PIN ASSIGNMENTS for REAR CONNECTOR (REAR VIEW SHOWN) - MEMORY ENABLE RETURN - MEMORY ENABLE 2 - MEMORY ENABLE 1 READ/WRITE - REFRESH CLOCK - GND. ARE GROUNDED ALL PINS ON

THIS SIDE

FIGURE 2.1

| LeCROY RE       | LeCROY RESEARCH SYSTEMS CORPORATION WEST NYACK, NEW YORK |

|-----------------|----------------------------------------------------------|

| S.MALM          | MODEL BROO                                               |

| CHECKED CHECKED | MEMORY MODULE                                            |

| 12 /2/FT        | BLOCK DIAGRAM                                            |

| 9 000000        | SHT.ZECO No.                                             |

#### SECTION 3

#### 3. FUNCTIONAL CIRCUIT DESCRIPTION

#### 3.1 General

-

-5

-

-3%

- D)

-5

-3

-

-

-

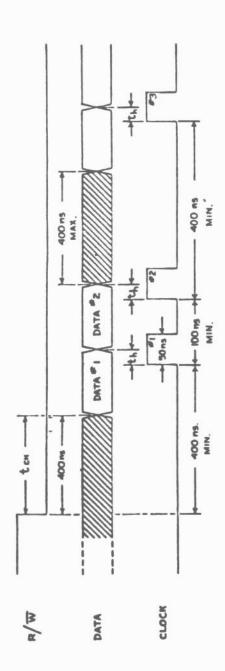

The LeCroy Model 8800A is a dual multiplexed memory consisting of 16K 12-bit words per memory bank (32K total). Write or read operations can be executed up to a 5 MHz average rate (see timing diagrams, Figures 3.1 and 3.2). The memory is only sequentially addressable when writing or reading. Since the 8800A uses 16K dynamic RAM's a minimum of 128 refresh pulses must be supplied every 2 msec. Refresh is accomplished by applying a 200 nsec (minimum) pulse to the refresh control line. The digitizer or memory controller module must generate this pulse at a time which ensures that memory read/write and refresh cycles do not overlap.

#### 3.2 Writing Data

After the memory has been initialized and enabled (see Figure 3.1) data can be written into memory. The first clock pulse will strobe data into the input storage register for Memory Bank #1 (see block diagram, Figure 3.3). The second clock pulse will strobe data into Memory Bank #2, transfer Memory Bank #1 storage register data to the input latch and initiate a 400 nsec memory cycle which stores data. This sequence continues until the memory is filled and MEM RTN or MEM1/2 is generated. After this time the internal logic will disable the memory write pulse.

#### 3.3 Reading Data

After the R/W control line changes state to a TTL low level, the 8800A will enter the readout mode (Figure 3.2). The R/W line transition initiates a memory readout cycle which loads data from the present memory address into Bank #1 and #2 output latches. At this time the input latches are disabled and Memory Bank #1's output latch is enabled onto the data bus. The first clock pulse will then disable Bank #1 output latch and enable Bank #2 output latch. The second clock pulse re-enables Bank #1 output latch, initiates a memory cycle and loads new data into the output latches. The sequence continues until the entire memory has been read out and MEM RTN or MEM1/2 is generated. After this time both output latches are disabled. (NOTE: During readout MEM RTN or MEM1/2 is generated immediately after the last two data words are stored in the output latches. The output latches will then automatically be disabled after the last two words have been readout).

FIGURE 3.1

manus BBDO - TD 1 must 1 10 C.C.

TIMING DIAGRAM

92/62/1

-37

D

•

0

0

3

0

0

Ď

5

3

3

3

GENERAL TIMING RULES! (WITH MEMORY WRITTEN INTO AS DESCRIBED IN 8800-TDI , SHEET I)

- I) to . NO REFRESH OR CLOCK PULSES ARE ALLOWED DURING THIS TIME OR THE 400 ns PRECEDING THE R/W TRANSITION.

- 2) DATA "I CORRESPONDS TO [LAST ODD DATA+I] WRITTEN INTO MEMORY.

3) th: ~ 20ns

4) REFRESH TIMING AND CONDITIONS SAME AS DURING WRITE OPERATIONS.

MEM. DA. RTH. ...

FIGURE 3.2

| S. MALM | -         | , ,      | ,      |

|---------|-----------|----------|--------|

| CHECKES | MODEL     | 000      |        |

|         | TINING    | DIAGR'   | 2 'N'. |

| 729/30  |           | OPERAT   | ZV-0:1 |

| 88      | 3800 TD I | 5 2 2 20 | 0000   |

LACTOY RESEARCH SYSTEMS

FIGURE 3.3